# Novel SPICE Macro Modeling for an Integrated Si Schottky Barrier Diode

Janam Ku<sup>1</sup>, Younghoon Min<sup>1</sup>, Donghyun Lee<sup>1</sup>, Iljong Song<sup>1</sup>, Dongsig Shim<sup>1</sup>, Namkyoung Lee<sup>1</sup>, Seonghearn Lee<sup>2</sup>, Yongtaek Lee<sup>2</sup>, Munsung Choi<sup>2</sup> and Jonghyck Kim<sup>2</sup>

<sup>1</sup> Samsung Advanced Institute of Technology, P.O. Box 111, Suwon 440-600, Korea Phone: +82-31-280-9438 FAX: +82-31-280-9473 E-mail: <u>kujanam@samsung.com</u>

<sup>2</sup> Department of Electronic Engineering, Hankuk University of Foreign Studies Phone: +82-31-330-4117 FAX: +82-31-330-4120 E-mail: <u>shlee@hufs.ac.kr</u>

*Abstract* — A new and accurate modeling has been performed for an integrated Schottky barrier diode fabricated by 0.18um standard CMOS process. The bulk and distributed effects are considered by adding macro elements to an original SPICE diode model. The resistance and capacitance model parameters have been obtained precisely by a direct extraction method using S-parameter sets with various bias points. The validity of this new model and parameter extraction method has been verified by comparing with the measured S-parameters over the wide range of bias up to 10GHz.

#### I. INTRODUCTION

Schottky barrier diode (SBD) has advantages of fast switching speed and low forward voltage drop. Due to these advantages, it has been used widely for low power rectifier or detector circuits in high-frequency range. Integrating Si SBD into CMOS RF IC is very important to increase high frequency performance as well as to decrease the production cost and chip size, in particular for fabricating dc voltage generator in a passive RFID chip where no dc supply is available [1], [2].

In order to design SBD rectifier or detector in a CMOS RF Transceiver chip, accurate and reliable simulation of DC and RF characteristics which are strongly dependent on the SPICE model and parameter extraction of the integrated Si SBD is required. Furthermore the input impedance in RF front-end block is very important for designing the matched printed antenna with the maximum transfer power. Generally the simple discrete SBD SPICE model has been used for commercial applications, however it is insufficient to describe the integrated Si SBD characteristics due to the bulk effect introduced by the lossy Si substrate as well as distributed effect of the lateral diode region in RF range.

Thus, a new integrated Si SBD SPICE model considering these bulk and distributed effects should imperatively be developed. In addition, accurate model parameter extraction is required to guarantee the reliable RF IC simulation. Typically, a general-purpose optimization process has been used to extract the large numbers of model parameters, however these additional parameters caused unphysical extraction results during optimization. To eliminate these unphysical errors, it is better to determine the model parameter using a direct extraction technique.

Therefore, in this paper, the new SPICE macro model for an integrated Si SBD and accurate direct parameter extraction method using measured S-parameters have been introduced, and the accuracy of the model and its parameter extraction technique has been verified from 0.1GHz to 10GHz.

## II. A NEW MODEL AND PARAMETER EXTRACTION

### A. New Model for Integrated SBD

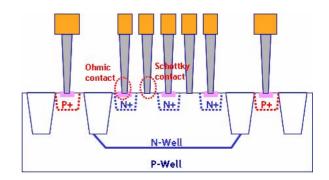

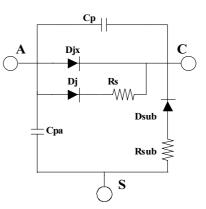

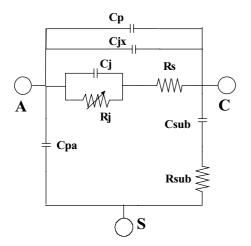

Fig. 1 shows the structure of the multi-finger integrated Si SBD fabricated with 0.18um standard CMOS process [3][4]. Figs. 2 and 3 show the newly developed SPICE macro model and its small-signal equivalent circuit.

Fig. 1. Fabricated Si Schottky Barrier Diode structure

Fig. 2. New SPICE macro model of the integrated Si SBD

Fig. 3. Small-signal Equivalent Circuit of the Si SBD

This macro model is composed of SPICE diode model and additional lumped components occurred by Si substrate. In addition, the internal junction diode Dj and the extrinsic junction diode Djx are separated to consider the lateral distributed effect happened in RF range dominantly. Cpa is the parasitic capacitance between the anode interconnection part and the substrate, Cp is the parasitic capacitance between anode and cathode. Dsub is the junction diode between n-well and p-substrate. Rsub is the resistance in the area of the substrate, Rs is the series resistance and Rj is the dynamic resistance of the diode junction. Cj and Cjx are intrinsic and extrinsic depletion capacitances in Dj and Djx respectively.

#### B. DC Parameter Extraction

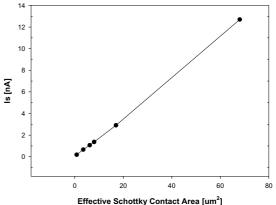

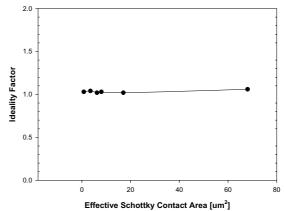

First of all, SPICE DC model parameters are directly extracted from the measured DC Id-V curves at some important points such as forward and reverse main turning points and the slope and y-intercept points of ln(Id)-V graph. Fig. 4 shows the extracted scalable saturation current Is according to the effective Schottky contact area and Fig. 5 notifies great uniform ideality factor regardless of the contact area of the fabricated Si SBDs.

The fabricated SBDs show soft breakdown characteristic which is one of the major elements that control the performance of the rectifier and are dominant in the reverse direction. For this soft breakdown modeling, we used the reverse bias SPICE parameters: reverse breakdown voltage BV, reverse breakdown ideality factor NBV, current at breakdown voltage IBV, low-level breakdown ideality factor NBVL, and low-level current at breakdown voltage IBVL.

Forward direction knee current (IKF) to model decrease of IV characteristic curve in high current, is extracted by the intersection point Id of fitting line having kT/q slope in the middle range of V and fitting line and having kT/2q slope in the high range of V in ln(Id)-V curve[6].

Fig. 4. Saturation current Is with scalability

Fig. 5. Ideality factor of Si SBDs with various contact area.

#### C. AC Parameter Extraction

For AC parameter extraction, a de-embedding technique has been performed to subtract the pad parasitic components from the measured S-parameters of the device [5].

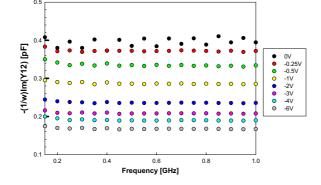

Generally MHz C-V measurement is used to extract capacitance, but the method is insufficient to measure very small junction capacitance Cj of the small sized Si SBD. Hence the direct RF extraction method which determines capacitance values using S-parameters measured in GHz range from the real devices has been developed in this work. Through this method, SPICE model parameters are extracted from the voltagedependent data of capacitance as follows.

Analysis in the low frequency range and under zero bias condition is very important because many internal parameters can be simplified reasonably. In Fig. 3, since Rj, Rs and Rsub may be ignored in the low frequency range(LF) at the zero bias(ZB) or reverse bias(RB), Cpa, Cp, Cj, and Csub can be approximated as follows.

$$(1/\omega) \operatorname{Im}(Y_{11}+Y_{12})_{LF} \approx Cpa$$

(1)

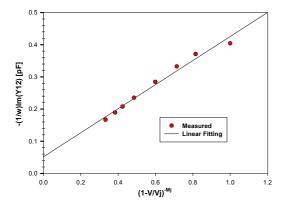

$$(-1/\omega) \operatorname{Im}(Y_{12})_{LF\&ZBRB} \approx Cp + Cj + Cjx$$

$$= Cp + (CJ+CJX)(1-V/Vj)^{-MJ}$$

(2)

$(1/\omega)$ Im $(Y_{22}+Y_{21})_{LF\&ZBRB} \approx Csub = CJS(1-V/Vjs)^{-MJS}$  (3)

where CJ, CJX and CJS are zero voltage junction capacitances, Vj and Vjs are built-in barrier voltages, MJ and MJS are capacitance grading factors. The zero or reverse bias values of Cpa and Csub are directly extracted from (1) and (3), respectively. After the voltage dependent data of  $-(1/\omega)Im(Y_{12})_{LF\&ZBRB}$  are obtained from Fig. 6, Cp is determined by finding y-intercept of  $-(1/\omega)Im(Y_{12})_{LF\&ZBRB}$  versus  $(1-V/Vj)^{-MJ}$ , as shown in Fig. 7. SPICE parameters such as Vj, Vjs, Mj, Mjs in (2) and (3) are extracted by simple curve fitting of the voltage dependent capacitance data.

Fig. 6. Measured  $-(1/\omega)$ Im(Y<sub>12</sub>) vs frequency at various V.

Fig. 7. Measured data and fitted line of  $-(1/\omega)Im(Y_{12})$  versus  $(1-V/Vj)^{-MJ}$ .

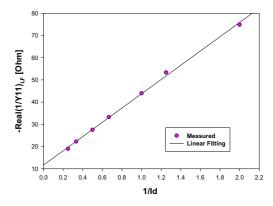

Conventionally, Rs is determined by fitting ln(Id) versus V curve deviated from the ideal line in high V [6], but this Rs extraction method using DC Id-V data includes uncertainty due to high current effect in the forward direction. In order to remove this uncertainty, the measured S-parameters at the same bias as the operation points are used to extract Rs. In the low frequency(LF), the value of Rs can be extracted simply by the following equation.

$$\operatorname{Real}(-1/Y_{11})_{LF} \approx \operatorname{Rs} + \operatorname{Rj} = \operatorname{Rs} + kT/qI_d \qquad (4)$$

Rs is determined without the extra extraction of Rj by the y-intercept point of the  $\text{Re}(-1/Y_{11})_{\text{LF}}$  data versus 1/Id in Fig. 8.

The separation of Cj and Cjx could be obtained by the direct method [7]. The fine tuning of CJ and CJX is performed by adjusting these extracted values to match  $S_{12}$  parameters with the measured ones. The extraction of Rsub is also can be obtained by a direct method using the slope of Re( $Y_{22}+Y_{12}$ )<sub>LF</sub> versus  $\omega^2$  data as follows:

$$\operatorname{Re}(Y_{22}+Y_{12})_{LF} \approx \operatorname{R_{sub}C_{sub}}^2 \omega^2$$

(5)

The optimal value of Rsub has been determined by changing the extracted value to match  $S_{22}$  parameters with the measured ones.

Fig. 8. Measured data and fitted line of  $-\text{Real}(1/Y_{11})_{LF}$  vs 1/Id.

## III. VERIFICATION OF MODEL ACCURACY

The accuracy of the new model and parameter extraction method explained above is verified by observing good agreement between the measured and modeled DC and S-parameters as follows.

# A. DC Verification

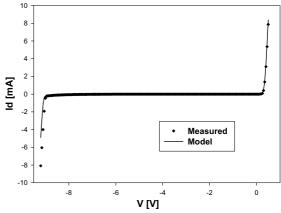

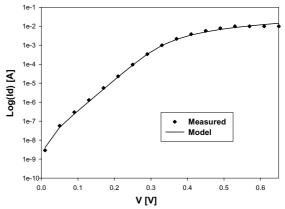

Figs. 9 and 10 show the accuracy of the DC simulation of the developed model.

Fig. 9. Measured and modeled DC Id-V characteristic curve.

Fig. 10. Enlarged forward DC Id-V characteristic curve.

# B. RF Verification

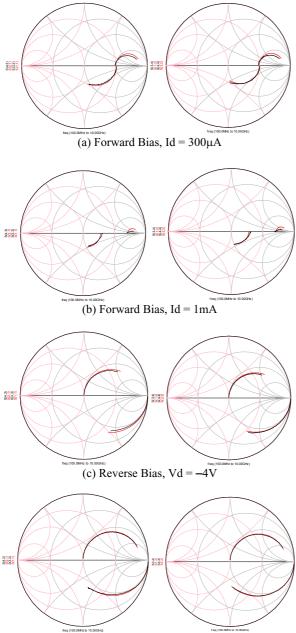

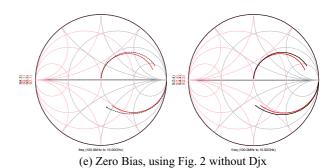

Figs. 11(a)-(d) show good correspondence between measured and modeled S-parameters from 0.1GHz to 10GHz at various bias points, verifying the RF accuracy of Fig. 2. In Fig. 11(d) and (e), modeled S-parameters of Fig. 2 with separated Dj and Djx are compared with those without Djx, and show much better agreements with measured ones at high frequencies. This clearly demonstrates the importance of the distributed model splitting Dj and Djx in RF range.

(d) Zero Bias, Vd = 0V

Fig. 11. Comparison between measured and modeled Sparameters at various bias points.

#### VI. CONCLUSION

We have developed the new SPICE macro model considering the lateral distributed and substrate effects in RF region for the integrated Si Schottky barrier diode, and a direct extraction method for AC model parameters using the measured S-parameters at GHz band. Using this extraction method, capacitances and resistances are accurately determined, and the model accuracy is verified in the wide range of bias up to 10 GHz.

#### ACKNOWLEDGEMENT

The authors wish to acknowledge the support of Smart Card Team colleagues in System LSI Division of Samsung Electronics, who make a valuable contribution to this work.

#### REFERENCES

- U. Karthaus, M. Fischer, "Fully intergrated passive UHF RFID transponder IC with 16.7-uW minimum RF input power," *IEEE Journal of Solid-State Circuits*, vol.38, pp. 1602, Oct. 2003.

- [2] J. Joe, M. Y. W. Chia, "Voltage, efficiency calculation and measurement of low power rectenna rectifying circuit," in *Proc. International Symposium of IEEE Antennas and Propagation Society*, Vol. 4, pp. 21-26 June 1998.

- [3] B. Rivera, R. Jacob Baker, J. Melngailis, "Design and layout of schottky diodes in a standard CMOS process," *Proceedings of the International Semiconductor Device Research Symposium*, pp. 79-82, 2001.

- [4] V. Milanovic, M. Gaitan, J. C. Marshall, and M. E. Zaghloul, "CMOS foundry implementation of Schottky diodes for RF detection," *IEEE Trans. Electron Device*, vol. 43, pp. 2210-2214, Dec. 1996.

- [5] S. Lee, "Effects of pad and interconnection parasitics on forward transit time in HBT's," *IEEE Trans. Electron Device*, vol. 46, pp. 275-280, 1999.

- [6] UTMOST Extraction Manual, Silvaco International, Santa Clara, CA.

- [7] S. Lee, "A Simple Method to Extract Intrinsic and Extrinsic Base-Collector Capacitances of Bipolar Transistors," *IEEE Trans. Electron Device*, vol. 51, no. 4, pp. 647-650, April 2004.