# A Converter MMIC with Integrated LO Amplifier and Doubler

Thomas A. Bös, Tomio Satoh\*, Kiyoshi Kajii\*, Edmar Camargo, Yuichi Hasegawa\*

Fujitsu Compound Semiconductor, Inc. 2355 Zanker Road, San Jose, CA 95131, USA

\* Fujitsu Quantum Devices Limited, Hachioji, Japan

Abstract — A highly linear converter MMIC with integrated LO amplifier and doubler is presented. Operating from a single 5V supply, the converter achieves 8 dB conversion loss as upconverter and 10dB as downconverter over the 21 - 32 GHz frequency band. With an IM3 suppression of – 50 dBc for Pin = 0 dBm, the converters are attractive for LMDS systems requiring high linearity.

#### **INTRODUCTION**

Fixed wireless access systems operating in the 21 to 32 GHz band have been developed for different applications of high data rate access, e.g. to bridge the "last mile" to the residential customer or to provide point to point communication between base stations. To achieve the high data rates, complex modulation schemes are required [1]. Those schemes demand a wide dynamic range from the converters used in the transceivers, to be able to handle the sudden changes in the signal level and still maintain the distortions within the standards. This problem is more emphasized in the receiver side, where a high LNA gain is required to mask the mixer noise, and a high IP3 is needed from the mixer to process high signal levels.

The upper input level limit for a wireless data receiver is -15 dBm [2]. Assuming the low noise amplifier provides 20 dB gain, then the mixer input power level will be 5 dBm. Typically 16 QAM signals require a C/IM3 suppression of 32 dB, which results in an input intercept point requirement of at least 21 dBm for the mixer. Thus, the receiver has to provide a very high intercept point mixer, which is the object of this paper.

Additionally, for systems integration it is essential that the number of high frequency components in the transceiver circuits can be reduced to a minimum, but still maintaining the flexibility for the user. To meet these targets the converter is integrated with LO amplifier and doubler circuits. The advantage of integrating a LO amplifier and doubler is the use of a lower LO frequency and lower LO input power. The MMIC operates from a 10 to 16 GHz LO source with a low input power of 0 to +3 dBm. Measured comparable mixers for the same frequency range usually have less functionality integrated and lower dynamic range [3,4].

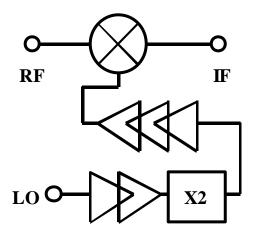

Fig. 1: Block diagram of the converter chip

#### **TOPOLOGY AND DESIGN**

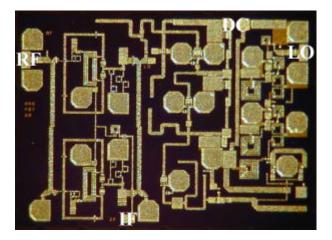

A block diagram of the fabricated MMIC containing a mixer, doubler and LO amplifier is shown in figure 1. The photo shown in figure 2 shows the chip layout, measuring  $3.1x2.2 \text{ mm}^2$ . It was fabricated with a  $0.25 \mu \text{m}$  pHEMT technology. The following section describes the design of the functional components.

### I) The Mixer

The mixer is a double single balanced mixer [5], where a planar spiral transformer is used to build a balun for a single balanced diode mixer. Two of those mixers are combined with Lange couplers, offering improved RF and LO return loss plus an L-to-R rejection in the order of 35 dB over a large band. On the RF side a good return loss is highly desirable to allow direct connection of image filter without degradation in its shape. On the LO side, a good return loss provides a good termination for the LO amplifier and improves conversion loss flatness for a wider range of LO drive. The Lange coupler is suited for this application for its performance and size combination. For this design, a 50 Ohm impedance for the Lange coupler was chosen.

Fig. 2: Photo of the converter chip

## **II) The LO Amplifier**

The LO driver operates under 3 dB gain saturation contributing to a better temperature performance and less sensitivity to the LO AM noise. In this design the LO amplifier consists of three stages with gate dimensions equal to  $4x50 \ \mu\text{m}^2$  in the first and second stages and  $6x50 \ \mu\text{m}^2$  in the third. The third stage gate area was a tradeoff between power gain flatness and ease of matching over the 21 to 32 GHz bandwidth. The amplifier operates from a single 5V supply voltage and all gates were self biased with a gate resistance to ground. Therefore, under saturation the gate current is limited guaranteeing reliability of the device. The bias resistor was also a key element in the stabilization of the amplifier.

## **III) The Doubler**

The challenge of the doubler design is the almost 50 % relative bandwidth required for the input signal. Conventional doubler designs, where a common source transistor biased at pinchoff and a short circuit at the drain for the LO feedthrough is

employed, do not achieve the required bandwidth. A topology based on a common gate and a common source transistor has been proved to be broadband [6] and has been selected for this design. The output filter was chosen to improve fundamental suppression. Additionally, a two stage amplifier was integrated to improve input match and reduce input power level requirements. This amplifier approximately delivers 15 dB of gain in the frequency range of 10 to 16 GHz. All matching networks are designed with spiral inductors and MIM capacitors. The doubler and the amplifier operate from a single 5V supply.

## **MEASURED RESULTS**

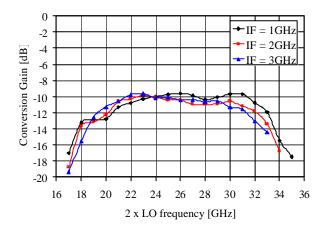

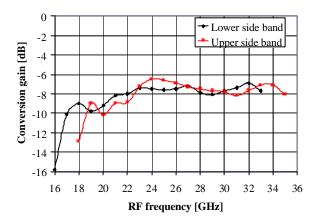

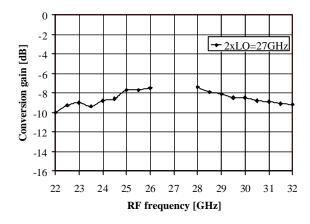

For all measurements a LO input power of +3 dBm was applied. The supply voltage was set to 5V. The convertion loss for the downconverter mode is in figure 3 for different IF frequencies. In the frequency band from 21 to 32 GHz the conversion loss is 10 dB. For a change in IF frequency from 1 to 3GHz the conversion loss remains essentially constant. The upconverter mode for the upper and lower sidebands were measured with an IF frequency of 1 GHz and are shown in figure 4. Over the band the typical conversion gain is -8 dB. The conversion gain versus IF frequency is shown in figure 5. In this measurement the LO frequency was fixed at 13.5 GHz and the IF signal was changed from 1 to 5 GHz. The conversion gain decreases less than 2 dB within the band.

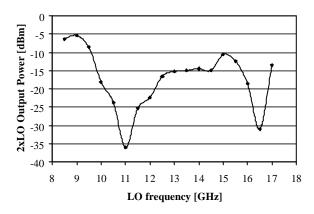

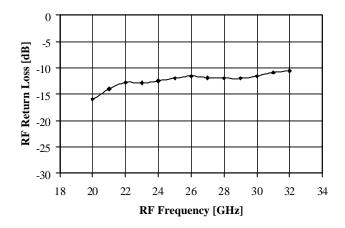

The output power at the second harmonic of the LO input frequency is shown in figure 6, expressed in absolute power level. The local oscillator input power at the fundamental is 3 dBm for this measurement. A decrease to 0 dBm did not degrade the mixer performance. The RF return loss is better than 10 dB over the frequency band from 21 to 32 GHz [figure 7]. Due to the lower frequency of the LO signal, matching at LO input frequencies was easier. A return loss better than 15 dB was measured.

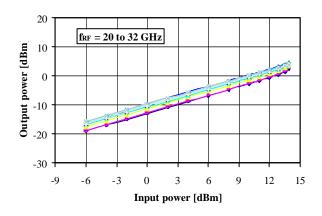

The power compression characteristic of the downconverter was measured with an automated measurement setup for input frequency from 21 to 32 GHz. As figure 8 shows, with the limited power range of the system, the mixer could not be compressed. Manual measurements at selected frequencies showed that the downconverter has a 1 dB compression point of +15 dBm. A 1 dB compression point of +15 dBm could also be measured for the upconverter. This good compression characteristic indicates the high

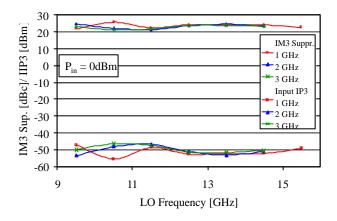

linearity of the converter. Intermodulation measurements were done for a two tone spacing of 10 MHz. The input intercept point and the third order intermodulation suppression is shown in figure 9. For an input 0 dBm power the upconverter and downconverter showed an IM3 suppression of -50 dBc with a resulting intercept point of +25dBm.

Fig. 3: Conversion gain of the downconverter for different IF frequencies

Fig. 4: Upper and lower side bands for the upconverter measured with 1 GHz IF frequency

Fig. 5: Conversion gain as a function of IF frequency for the upconverter with  $f_{LO} = 13.5$  GHz

Fig. 6: LO output power of the second harmonic of the LO frequency at the RF port

Fig. 7: RF return loss versus frequency

Fig. 8: Power compression of the down-converter

Fig. 9: Input intercept point and IM3 suppression measured at Pin = 0 dBm for different IF frequencies and 10 MHz signal spacing

#### CONCLUSION

The design and measured results of a MMIC integrating a highly linear diode frequency converter, a LO amplifier and doubler on a single chip are reported. For an LO input frequency ranging from 10 to 16 GHz, the MMIC operates as

up- or downconverter over the 21 - 32 GHz RF band. The measured input intercept point is +25dBm over the bandwidth, which makes the converter suitable for highly linear applications. With a typical C/IM3 system requirement of – 32 dB for 16 QAM signals, the mixer has to be able to convert input signals up to 9dBm. This input level is lower than the measured 1dB compression point of 15dBm.

#### REFERENCES

[1] B. H. Walke *et al.*, "IP over Wireless Mobile ATM-Guaranteed Wireless QoS by HiperLAN/2", Proc. of IEEE, vol. 89, no. 1, pp. 21-40, January 2001

[2] ETSI, "Transmission and Multiplexing (TM), Digital fixed point-to-point radio link equipment operating in the frequency range 24,25 GHz to 29,50 GHz", ETS 300431, 1996

[3] L. Verweyen *et al.*, "LMDS Up-and Down-Converter MMIC" 2000 IEEE MTT-Symp. Digest, Boston, USA, pp. 1685-1688

[4] K. Kawakami, M. Shimozawa, H. Ikematsu, K. Itoh, Y. Isota, O. Ishida, "A millimeter-wave broadband monolithic even harmonic inage rejection mixer" 1998 IEEE MTT-Symp. Digest, pp. 1443-1446

[5] R. S. Virk, T. A. Bös, E. Camargo, Yuichi Hasegawa, "High Dynamic Range MMIC Converters for LMDS Applications", European Gallium Arsenide & Other Semiconductor Application Symposium GAAS 2001, September 2001, London, United Kingdom, pp. 69-72

[6] T. Hiraoka, T. Tokumitsu, M. Akaike "A Miniaturized Broad-Band MMIC Frequency Doubler", IEEE Trans. on MTT., Vol. MTT-38, No. 12, Dec. 1990, pp. 1932-1937