# On-wafer I/V measurement setup for the characterization of low-frequency dispersion in electron devices

A.Raffo<sup>•</sup>, A.Santarelli <sup>o</sup>, P.A.Traverso <sup>o</sup>, G.Vannini <sup>•</sup>, F.Filicori <sup>o</sup>

- Department of Engineering, University of Ferrara, Via Saragat 1, 44100 Ferrara, Italy, e-mail: araffo@ing.unife.it, gvannini@ing.unife.it.

- Department of Electronics, University of Bologna, Viale Risorgimento 2, 40136 Bologna, Italy, e-mail: ptraverso@deis.unibo.it, asantarelli@deis.unibo.it, ffilicori@deis.unibo.it.

Abstract — Large-signal dynamic modelling of III-V FETs cannot be simply based on DC i/v characteristics, when accurate performance prediction is needed. In fact, dispersive phenomena due to self-heating and/or traps (surface state densities and deep level traps) must be taken into account since they cause important deviations in the low-frequency dynamic drain current. Thus, static drain current characteristics should be replaced with a suitable model which also accounts for low-frequency dispersive effects. The research community has proposed different modelling approaches and quite often a characterisation by means of pulsed i/v measurement systems has been suggested as the more appropriate for the identification of lowfrequency drain current models. In the paper, a new largesignal measurement setup is presented which is based on simple low-frequency sinusoidal excitations and it is easily reproducible with conventional general-purpose lab instrumentation. Moreover, the proposed setup is adopted in the paper to extract a backgating-like model for dispersive phenomena.

Index Terms — Field effect transistors, semiconductor device characterisation, large-signal modeling, dispersive phenomena.

## I. INTRODUCTION

Accurate nonlinear modelling of III-V FETs for microwave circuit design should also account for lowfrequency dispersive phenomena of the electrical characteristics due to deep level traps and surface state densities. Moreover, time constants associated with dynamic phenomena due to thermal effects, although somehow longer, are not always so much different from those associated with traps or surface states (typically from fractions to hundreds of microseconds). Consequently, dispersion due to traps cannot always be addressed separately from thermal phenomena due to power dissipation. All those phenomena cause considerable deviations between static and low frequency

dynamic drain current characteristics<sup>1</sup>, which cannot be ignored when accurate nonlinear models are needed. Many efforts have been made by several research groups to take into account low-frequency dispersion both in mathematical and equivalent circuit models. As well known, beside DC and small-signal measurement data some modelling approaches need pulsed i/v measurements during the identification phase for improved prediction accuracy. In fact, pulsed measurement systems allow for a wider low-frequency dispersion characterisation under large-signal operation.

As well known, the main advantage of dynamic i/v largesignal measurements carried out through the application of very short<sup>2</sup> voltage pulses consists in preserving the mean values of junction temperature and applied voltages almost equal to the corresponding quiescent values during the acquisition time. Unfortunately, application of voltage pulses also presents some drawbacks. For example, a critical point is related to the extremely wide spread of the pulsed-waveform spectral components. In fact, biasdependent spectra of device-under-test (DUT) input and output impedances, bandwidth limitation of cables, bias networks and other components of the measuring setup may actually "extend" the real duration of pulses in such an almost unpredictable way. This leads to critical calibration procedures and difficult evaluations of the correct sampling times for current acquisitions, limiting to some extent the achievable measurement accuracy. This aspect is particularly important when highly accurate

<sup>1</sup> The "low-frequency" term is used here referring to the frequency range between the upper cutoff of dispersive phenomena and the lowest frequency where reactive effects, related to charge storage variations and finite transit times, cannot be further neglected.

<sup>&</sup>lt;sup>2</sup> Compared to typical time constants of dispersive phenomena (e.g., typical pulse duration  $< 1 \mu s$ ).

modelling of the *i/v* dynamic behaviour is needed as for intermodulation prediction.

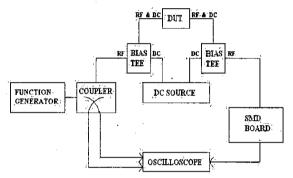

In the paper an alternative large signal i/v measuring system is presented (Fig.1) where the DUT is simply excited by a low frequency large-signal sinusoidal voltage source having  $50\Omega$  internal impedance and it is loaded by selectable resistive impedances. A digital sampling oscilloscope allows for the acquisition of the incident and reflected waves at the transistor ports. Full automatic remote controlling software through a standard IEEE488 interface was developed in order to "dynamically reach", with maximum peak amplitude values of the input and output device voltage waveforms, an arbitrary grid over the (vg, vd) domain. On wafer measurement data taken with the proposed instrumentation on a 0.25µm GaAs PHEMT (W=600µm) are then used for the identification of a backgating-like model [1] for low-frequency dynamic drain current deviations.

Fig. 1. The proposed large-signal measurement setup.

# II. THE NEW LARGE-SIGNAL I/V MEASUREMENT SETUP.

The on wafer measuring system shown in Fig.1 is here briefly described. The two independent output channels of an arbitrary function generator are used one for feeding the DUT with a sinusoidal voltage waveform in the frequency range 2-12MHz and the other one for triggering the oscilloscope data acquisitions. To this aim, a digital oscilloscope with four input channels, each one sampled up to 4GSa/s, is used. Moreover, a high resolution (4μV; 20fA) highly accurate (V: 0.05%, 1: 0.2%) DC source provides the bias for the DUT. Monitoring of incident and reflected waves at the DUT input is obtained by means of a wide bandwidth (10kHz – 1000MHz) dual directional coupler, while 100kHz–6000MHz bandwidth bias-tees with low insertion loss (0.15dB) are used for suitable DC and RF path isolation and also for ensuring stability. In

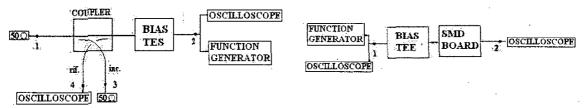

order to provide different, purely resistive DUT loading conditions, SMD-type resistors having different values were mounted on FR4-substrate boards and "series" wired through  $50\Omega$  transmission lines to external SMA connectors (the total loading resistance obtained being the SMD resistor value plus the  $50\Omega$  oscilloscope input impedance). Minimum phase rotations are obtained by connecting the selected board as close as possible to the drain probe, as shown in Fig.2.

Fig. 2. Detail of the measurement system. From left to right: GSG probe tip on thermal chuck, bias-tee, FR4-substrate-based board with mounted SMD resistor.

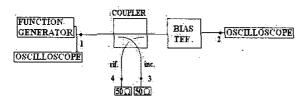

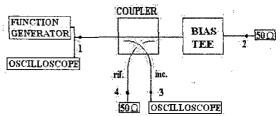

The simplicity of the system presented is its major advantage. In fact, at the frequency of a few MHz all the measuring system components satisfy linear nondistortion conditions, greatly simplifying the needed calibration procedure. To this aim, the setup can be divided into four signal paths, as shown in Fig.3, which can be characterised in terms of attenuations and delays in the working frequency range: a) from signal generator output section to DUT input; b) from signal generator output section to oscilloscope section (incident wave input); c) from DUT input section to oscilloscope section (reflected wave input); d) from DUT output section to oscilloscope section. Table I shows the characterisation data measured for the calibration of each path in Fig.3. In particular, mean values of the attenuation and delay of each signal path over the frequency range 2-12 MHz are reported.

| Path             | a   | ь   | с   | d   |

|------------------|-----|-----|-----|-----|

| Delay (ns)       | 7.3 | 2.9 | 7.3 | 6.2 |

| Attenuation (dB) | 0.3 | ≈0  | 0.3 | 0.2 |

Tab. I. Characterisation of the measurement setup in the frêquency range: 2-12MHz.

a) from signal generator output section to DUT input.

b) from signal generator output to input incident-wave measurement section.

- c) from DUT input to input reflected-wave measurement section.

- d) from DUT output to transducer-wave measurement section.

Fig.3 Calibration in terms of attenuation and delay of the four different signal paths associated with the proposed largesignal measurement setup.

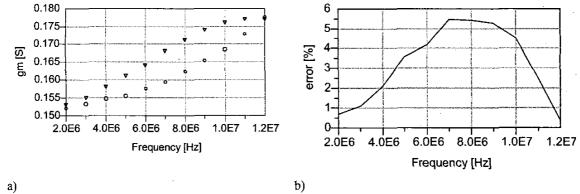

Fig. 4. On-wafer measured small-signal trans-conductance (with  $50\Omega$  load) of a  $0.25\mu m$  GaAs PHEMT (W= $600\mu m$ ), biased at VGS=-0.6V, VDS=4V: (a) comparison between the proposed measurement setup (triangle) and a conventional VNA (circle); (b) relative deviation between the two measurements.

Observed delay deviations from the mean values shown in the table were less than 5% over the whole frequency range while the attenuation deviations were almost negligible. The return loss at the input and output ports of each signal path were also measured, always obtaining more than 40dB. This further confirms that a simple characterisation of the described signal paths in terms of corresponding attenuation and delay is accurate enough at operating frequencies of a few MHz.

The accuracy of the described measurement setup has been tested under small-signal conditions. In particular, the dynamic trans-conductance of a 0.25  $\mu$ m GaAs PHEMT (W=600 $\mu$ m), biased at V<sub>GS</sub>=-0.6V, V<sub>DS</sub>=4V, was measured under small-signal sinusoidal excitation and 50 $\Omega$  loading conditions by means of a vector network analyser in the 2-12MHz frequency range. The obtained results were then compared with the corresponding quantities measured with the proposed measurement setup. The agreement found and the corresponding relative deviation, always better than  $\pm 6\%$ , are shown in Fig.4. The ability to measure both small-signal (with comparable accuracy to conventional network analysers)

and large-signal data without modifications in the instrument configuration represents an important advantage of the proposed setup. As far as the large-signal data acquisition is concerned, different operation modes are possible depending on parameter settings such as the quiescent condition:  $(V_{g0}, V_{d0})$ , the peak amplitude of the sinusoidal waveform and the loading resistor value. Moreover, since operating conditions must be respectful of the DUT Safe Operating Area (SOA) a suitable controlling algorithm has been defined. To this aim, the

measurement setup was controlled via an IEEE488 standard interface by means of commercial instrument automation software running on a PC (LabVIEW).

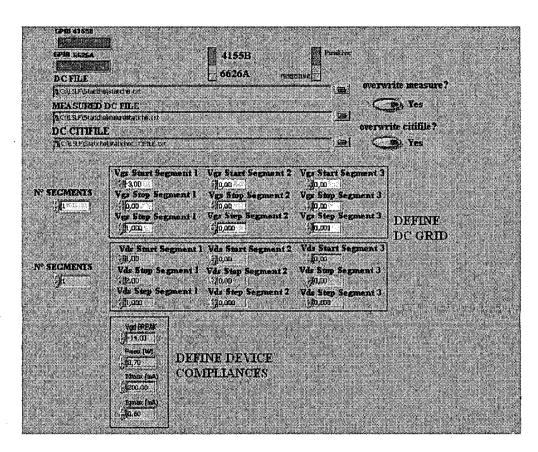

The control-software front-panel section aimed at the DC DUT characterisation is shown in Fig. 5. Piece-wise uniform grid of bias voltages may be here defined and the main compliances limiting the device SOA must be specified. In particular, breakdown voltage, maximum dissipated power, maximum gate and drain currents are entered at this stage.

Fig. 5. Main input panel of the LabVIEW control software section aimed at DC characterisation.

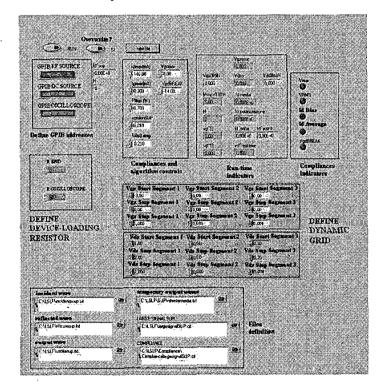

The front-panel of the control program section aimed at the dynamic measures is shown in Fig.6. The program asks the user for the grid of  $(v_g, v_d)$  points in the domain of instantaneous device port voltages to be "dynamically reached" and for the value of the device loading resistor. Although the proposed large-signal measurement system could be likely exploited for dynamic behaviour testing outside the static SOA, at the moment we limited the grid of dynamic voltage pairs to be a subset of the static grid. On this basis, a small-signal measurement around each

point of the dynamic voltage grid is always also carried out and available for model identification purpose.

The developed LabVIEW control program searches for two sets of bias voltages and suitable corresponding amplitudes of the input sinusoidal waveform iteratively for each point of the specified dynamic voltage grid. In particular the program works satisfying the following rules: 1) the "destination" point in the  $(v_g, v_d)$  domain must be reached with a peak value (maximum or minimum) of the device port voltage waveforms; 2) the amplitude of the

applied sinusoidal waveform must be as large as possible; 3) all the DUT compliances must be respected under dynamic conditions. In particular, a more accurate measurement is carried out by choosing to sample the peak values of the currents. In fact, on the basis of a uniformly-spaced time scale, more dense samples in the neighbourhood of peak values are obtained and special-purpose functions of digital sampling oscilloscopes may also be efficiently exploited for the acquisition. Moreover, maximum amplitude of the applied sinusoidal voltage guarantees operation under the largest signal condition allowed, i.e., a condition as much as possible different

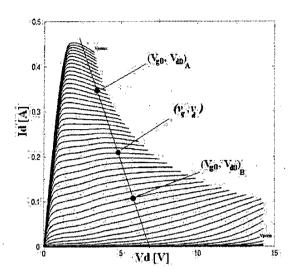

from the small-signal measurement, which in general is also carried out around each  $(v_g, v_d)$  point. Finally, a conservative choice has been done by limiting the dynamic SOA under dynamic conditions to the corresponding area defined for the DC characterisation. The two sets of bias conditions found for each dynamic voltage pair, will be referred to in the following as A-type (upper-bias) and B-type (lower-bias) as shown in Fig.7. Unfortunately, the operation described in that figure only applies to an ideal non-dispersive device, where no difference exists between DC and low-frequency AC drain current characteristics.

Fig. 6. Main input panel of the LabVIEW control software for dynamic measurements.

In fact, dispersion due to traps and thermal phenomena cause important deviations between static and low frequency dynamic drain current characteristics, which are strongly dependent on the quiescent conditions. Thus, a more realistic situation is described in Fig.8, where three different drain current values are shown for a generic  $(v_g, v_d)$  dynamic voltage pair: the DC current (laying on the DC characteristic obtained for  $V_{g0} = v_g$ , represented by the middle curve in Fig.8) and two dynamic values corresponding to the large-signal dynamic operation with the A- and B-type bias respectively. These two values lay on dynamic drain characteristics (upper and lower

characteristics in Fig.8) obtainable through a dynamic measurement system with the A- and B-type bias respectively.

The outlined measurement procedure may be repeated for different values of the loading resistor, obtaining a suitably large set of dynamic current measurements for any  $(v_g, v_d)$  voltage pair. Eventually, all the data concerning bias and amplitude of the applied voltage waveform and loading condition corresponding to each current acquisition are collected in suitable files to be used in subsequent model identification.

Fig. 7. PHEMT DC drain current characteristics. Two suitable sets of bias voltages (A, B in the figure) are searched for each  $(v_g, v_d)$  instantaneous voltage pair to be *dynamically reached* (see text).

# Fig. 8. Three different drain current values, associated with the same $(v_g, v_d)$ voltage pair. The middle value corresponds to the DC current; the upper and lower dynamic values are obtained by the large-signal measurement setup using the A and B bias conditions (see text).

$(V_{g0}, V_{d0})_A$

P

Dynamic Current (I<sub>D</sub>)<sub>A</sub>

> Static Current (I<sub>D</sub>)<sub>de</sub>

> > Dynamic Current  $(\mathbf{I_D})_{\mathbf{B}}$

$(V_{e0}, V_{e0})_{p}$

# III. IDENTIFICATION OF A LOW-FREQUENCY DRAIN CURRENT MODEL.

The proposed measurement system was used for the identification of a backgating-like model for the low-frequency drain current in III-V devices [1]. In particular, according to [1], the drain current is expressed as:

$$i_d(t) = [1 + K(p_s(t) - P_0)] \cdot F^{DC} \{v_{cc}(t), v_d(t)\}$$

(1)

where:

$$v_{ex}(t) = v_{e}(t) + \alpha_{e}(v_{e}(t) - V_{e0}) + \alpha_{d}(v_{d}(t) - V_{d0}). \tag{2}$$

In (1) and (2),  $V_{g0}$ ,  $V_{d0}$  are the average values of the applied voltages  $v_g(t)$ ,  $v_d(t)$ , respectively, and  $\alpha_g$ ,  $\alpha_d$ , K are suitable scalar coefficients to be determined. Moreover,  $P_0$  represents the average dissipated power under dynamic conditions and  $p_s(t)$  is a "quasi-static" power corresponding to the power that would be dissipated if  $v_g(t)$ ,  $v_d(t)$  were "slowly" time-varying voltages. In [1] it is shown how the identification of the three parameters  $\alpha_g$ ,  $\alpha_d$ , and K may be carried out on the basis of DC and small-signal conductance measurements. In fact, linearisation of (1)-(2) with respect to  $v_g(t)$  and  $v_d(t)$  around a generic bias condition ( $V_{g0}$ ,  $V_{d0}$ ) leads to:

$$g_{m}^{AC} \left\{ V_{g0}, V_{d0} \right\} = \left[ 1 + k \cdot V_{d0} \cdot I_{d0} + \alpha_{g} \right] \cdot g_{m}^{DC} \left\{ V_{g0}, V_{d0} \right\}$$

(3)

$$g_{d}^{AC} \left\{ V_{g0}, V_{d0} \right\} = \left[ 1 + k \cdot V_{d0} \cdot I_{d0} \right] \cdot g_{d}^{DC} \left\{ V_{g0}, V_{d0} \right\} +$$

$$+ k \cdot I_{d0}^{2} + \alpha_{d} \cdot g_{m}^{DC} \left\{ V_{g0}, V_{d0} \right\}$$

$$(4)$$

where  $g_m^{\ AC}$ ,  $g_d^{\ AC}$ ,  $g_m^{\ DC}$ ,  $g_d^{\ DC}$  represent the trans- and output-conductance under low-frequency (AC) and static (DC) conditions, respectively, while  $I_{d\theta}$  is the DC drain current. Minimisation on a suitable grid of bias conditions of the discrepancies between measured dynamic conductances and (3)-(4) leads to the identification of the three unknown model parameters. We will refer to this model as "SS-backgating" to stress that the identification procedure is based on DC and small-signal measurements only. Instead, the three model parameters were identified in this work by also adding an "extra" constraint on the coherence between (1)-(2) and corresponding large-signal dynamic current measurements obtained through the setup described in the previous section and using two different values of the loading resistors. To this aim, a least-square minimisation was carried out in the framework of the CAD tool Agilent ADS. We will refer to this model extraction as "LS-backgating".

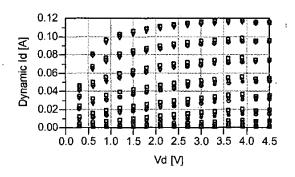

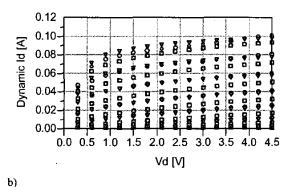

a) b) Fig. 9. Large-signal dynamic current of a GaAs  $0.25\mu m$  PHEMT ( $50\Omega$  load). Measurements (circles) obtained with the proposed large-signal setup using the A-type (a., left) and B-type (b., right) bias as described in the text; predictions based on SS-backgating (squares) and LS-backgating (triangles) models.

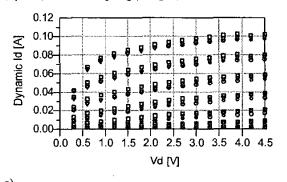

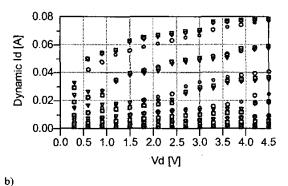

Fig. 10. Large-signal dynamic current of a GaAs  $0.25\mu m$  PHEMT (320 $\Omega$  load). Measurements (circles) obtained with the proposed large-signal setup using the A-type (a., left) and B-type (b., right) bias as described in the text; predictions based on SS-backgating (squares) and LS-backgating (triangles) models.

In order to identify the SS- and LS-backgating models for a 0.25  $\mu$ m GaAs PHEMT (W=600  $\mu$ m), on-wafer measurements were carried out under static and dynamic conditions using the proposed setup. In particular, large-signal measurements were carried out using two different loading resistors,  $50\Omega$  and  $320\Omega$ . A suitably large number of static and dynamic voltage pairs was considered for model identification, sweeping the  $(v_g, v_d)$  domain with 0.1V and 0.3V steps in  $v_g$  and  $v_d$  respectively. The extracted coefficients of the SS- and LS-backgating models are reported in Table II.

In Fig.9 and 10, large-signal measurements (circles) carried out with the new measurement system using  $50\Omega$  and  $320\Omega$  resistors, respectively, are shown. Measurements refer to the values of the dynamic drain currents obtained using the A-type and B-type bias. Dynamic drain current predictions obtained by means of the SS-backgating (squares) and LS-backgating (triangles) models are also shown in Figs.9 and 10. A pretty good

prediction capability of the models can be observed; in this context it must be outlined the extremely restricted number of model parameters (only three) adopted to describe the very complex low frequency dispersive behaviour. As expected, an evident, better prediction accuracy is obtained by means of the LS-backgating which exploits also large-signal measurements for the identification of model coefficients.

|        | $a_g$   | $a_d$  | K     |

|--------|---------|--------|-------|

| LS-BKG | -0.0155 | 0.0172 | 0.053 |

| SS-BKG | -0.124  | 0.0088 | 0.272 |

Tab.II Extracted model coefficients for the Backgating model (1-2) proposed in [1].

### IV. CONCLUSION

In this paper a new large-signal i/v measurement setup has been presented and its hardware/software implementation was described in detail. The most important features of the system proposed are the utilization of only conventional general-purpose lab instrumentation and its simplicity. The latter allows to overcome some of the problems related to the utilization of other non-standard dynamic i/v measurement systems (e.g., pulsed i/v setups).

The measurements carried out with the new setup have also been used to identify a Backgating-like model for a  $0.25\mu m$  GaAs PHEMT. The comparison between measurements and model prediction confirms the accuracy improvement of the model identified on the bases of large-signal i/v measurements with respect to the same model extracted on the basis of only small-signal measurements.

### ACKNOWLEDGEMENT

This work was partly funded by MIUR (Italian Ministry of Instruction, University and Research) and also performed in the context of the network TARGET – "Top Amplifier Research Groups in a European Team" supported by the Information Society Technologies Programme of the EU under contract IST-1-507893-NOE, www.target-net.org.

# REFERENCES

[1] A.Santarelli, G.Vannini, F.Filicori, P.Rinaldi "Backgating model including self-heating for low-frequency dispersive effects in III-V FETs", Electronics Letters 1st October 1998 Vol.34 No.20.

- [2] A.Costantini, P.A.Traverso, G.Favre, M.Pagani, A.Santarelli, G.Vannini, F.Filicori, "Accurate prediction of PHEMT intermodulation distortion using the nonlinear discrete convolution model", IEEE MTT-S, International Microwave Symposium, Seattle, Washington, USA, June 2-7, 2002.

- [3] J.A.Reynoso-Hernandez, L.Escotte, R.Plana, J.Graffeuil "Deep level characterisation in GaAs FETs by means of the frequency dispersion of the output impedence", Electronics Letters 13th April 1995 Vol.31 No.8

- [4] J.M.Golio. M.G.Miller, G.N.Maracas, D.A.Johnson "Frequency-Dependent Electrical Characteristics of GaAs MESFET's", IEEE Transactions On Electron Devices, Vol.37 No.5, May 1990.

- [5] J.Verspecht "Calibration of a Measurement System for High Frequency Nonlinear Devices", Doctoral Dissertation, 1995

- [6] N.Scheinberg, R.Bayruns, and R.Goyal, "A low frequency GaAs MESFET circuit model", IEEE J. Solid-State Circuits, 1988, Vol.23, N.2.

- [7] K.Lu, P.McIntosh, C.M.Snowden, R.D.Pollard, "Low-Frequency dispersion and its influence on the Intermodulation performance of AlGaAs/GaAs HBTs". IEEE MTT-S Digest, 1996.

- [8] T.Roh, Y.Kim, Y.Suh, W.Park, B.Kim, "A simple and accurate MESFET channel-current model including biasdependent dispersion and thermal phenomena", IEEE Trans. on MTT, 1997, Vol.45, N.8.

- [9] P.H.Ladbrooke, S.R.Blight, :"Low-Field Low-Frequency Dispersion of Transconductance in GaAs Mesfet's with Implications for Other Rate-Dependent Anomalies". IEEE Transactions On Electron Devices, Vol.35 No.3 March 88.

- [10] J.Rodriguez-Tellez, T.Fernandez, A.Mediavilla, A.Tazon, "Characterisation of Thermal and Frequency-Dispersion Effects in GaAs MESFET Devices", IEEE Trans. on MTT, Vol.49, No.7, July 2001.