# ICs for 100 Gbit/s Data Transmission

Koichi Murata, Takatomo Enoki, Hirohiko Sugahara, and Masami Tokumitsu

NTT Photonics Laboratories, NTT Corporation 3-1 Morinosato Wakamiya, Atsugi, Kanagawa, 243-0198 Japan Phone: +81 46 240 2871, Fax: +81 46 240 2872, e-mail: murata@aecl.ntt.co.jp

Abstract — Research and development of InP-based transistors and integrated circuits (ICs) are driven by applications in millimeter-wave wireless and broadband optical fiber communications systems. This paper describes our research activities on InP HEMT and HBT IC technologies for optical communications systems and discusses the future prospects and technical issues of ICs for 100 Gbit/s and beyond.

#### I. INTRODUCTION

IC technology has contributed to the development of economical high-speed optical communications systems. Up to now, 40-Gbit/s SONET/SDH [1] and OTN [2] frame formats have been standardized for telecommunications systems, while 10-Gbit/s Ethernet has been standardized for data communications systems. The interface speeds of telecommunications and data communications systems have increased by a factor of 4 and 10, respectively. This means that, if current trends continue, the next-generation interface speeds will be 160 Gbit/s for the former and 100 Gbit/s for the latter. Work on the technological aspects of 40-Gbit/s ICs has reached the stage where cost-effective commercial products are being developed, and dominant competing technologies are InP HBT and SiGe HBT in this area. The possibility of realizing 100-Gbit/s class ICs based on InP HEMTs and InP HBTs for next-generation systems is now being

This paper describes recent progress in our InP-based IC technologies and discusses their future prospects. After overviewing the optical transmission front-end ICs, we present the current status of our InP HEMT and InP HBT device technologies with some of our latest IC results and also discuss future prospects of IC technologies for 100-Gbit/s and beyond.

# II. OVERVIEW OF OPTICAL TRANSMISSION FRONT-END $$\operatorname{ICs}$$

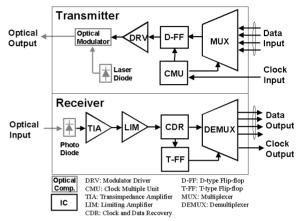

Figure 1 shows an example of the basic transmitter and receiver configurations. The clock multiplier unit (CMU) and the clock and data recovery circuit (CDR) are usually based on a phase-locked loop consisting of a voltage controlled oscillator (VCO), a phase comparator, a low pass filter, and a D-type flip-flop (D-FF). Analog ICs in the receiver like the transimpedance amplifier (TIA) and limiting amplifier (LIM) are generally required for 70 % bandwidth of the data rate with flat phase characteristics [3], while the modulator driver (DRV) in the transmitter requires both broadband characteristics

Fig. 1. Basic transmitter and receiver configurations.

and high saturation output power. As for digital ICs, such as multiplexer (MUX) and demultiplexer (DEMUX), switching operation at the data rate is required. Figure 1 shows an example of a full-rate system, which means the D-FF and CDR operate at the data rate with a clock signal that is the same as the data rate. In this system, the D-FF and CDR are critical components, and they limit system speed because of their full-rate clock operations. A system in which the D-FF is eliminated and CDR operates with the half the data-rate clock (referred to here as a half-rate system) mitigates the speed requirement for the electrical components. The full-rate system is, however, superior to the half-rate system in the system margin and robustness. Up to now, basic 100-Gbit/s front-end ICs, such as baseband amplifiers [4,5], a static frequency divider [6], MUX [7,8], and VCO [9,10], have been demonstrated. Dominant technologies in 100-Gbit/s-class ICs are currently InP-based HEMT and HBT.

#### III. CURRENT STATUS OF NTT'S INP-BASED ICS

### A. InP HEMT ICs

We have developed InP-based HEMT IC technology for 40-Gbit/s optical communications systems. The IC integrates 0.1- $\mu$ m-gate-length InAlAs/InGaAs/InP HEMTs, InAlAs Schottkey diodes, metal resistors, MIM capacitors, and two-level interconnection lines with a low-permitivity interlayer [11]. Typical average threshold voltage is -0.5 V, and the standard deviation is low at around 13 mV for a 3-inch wafer. The typical transconductance (gm) is 1.2 S/mm, and the current gain cut-off frequency ( $f_{max}$ ) are 186 and 320 GHz, respectively.

Table 1 summarizes the performance of the 40-Gbit/s InP HEMT ICs [12]. We have developed a TIA, a LIM, distributors for data signal and clock signal, a fully monolithic integrated CDR, a D-FF, a T-type flip-flop (T-FF), and a low-power 4-bit MUX and DEMUX to construct the optical transmitter and receiver shown in Fig. 1. The analog ICs offer sufficient performance for 40-Gbit/s applications, while the digital ones exhibit error-free operation at up to 50 Gbit/s. All of the 40-Gbit/s electrical components except for the modulator driver can be made by using InP HEMT technology. Reliability tests have already been performed for small-scale ICs, and the lifetime of the T-FF IC is 1 x 10<sup>6</sup> h at the junction temperature of 100 degrees centigrade [13].

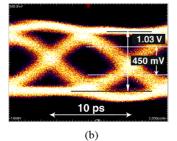

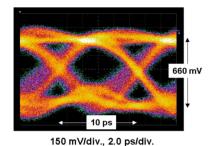

To investigate the possibility of making 100-Gbit/sclass ICs, we first examined the multiplexing operation of a 2-bit MUX and the demultiplexing one of a D-FF using the InP HEMTs. To boost MUX circuit speed, we devised a selector core so that it can directly drive the external 50- $\Omega$  load. Figures 2(a) and (b) show a chip photograph of the MUX IC and its operating waveform at 100 Gbit/s. Clear eye opening is obtained with the output voltage of 1.03 V and the eye height of 450 mV. Error-free operation for a 2<sup>23</sup>-1 PRBS signal is also confirmed at 100 Gbit/s by using a test chip that contains the MUX and the D-FF. These results confirm that both the 100-Gbit/s multiplexing operation of the MUX IC and the 100-Gbit/s demultiplexing operation of the D-FF were successfully achieved [7]. The current 0.1-µmgate-length InP HEMT has a potential to construct halfrate 100-Gbit/s systems.

TABLE 1

PERFORMANCE OF INP HEMT ICS

| Circuit       | Operating Speed                                                               | Output (Vpp) | Power (W) |

|---------------|-------------------------------------------------------------------------------|--------------|-----------|

| TIA           | Zt= 48.2 dB $\Omega$ , $f_{3dB}$ = 43 GHz                                     | 0.46         | 0.35      |

| Limiting Amp. | Gain= 25.4 dB, f <sub>3dB</sub> = 32 GHz<br>DC - 50 Gbit/s, Sens.: 27 mV @43G | 1.3          | 0.6       |

| Distributors  | Data: DC - 50 Gbit/s                                                          | 1.1          | 1.6       |

|               | Clock: 2 - 47 GHz                                                             | 1.0          | 0.5       |

| CDR           | 43 Gbit/s, Sens.: 175 mV                                                      | 1.2          | 2.8       |

| D-FF          | 20 - 50 Gbit/s<br>P.M.: 101 deg. @50G                                         | 0.9          | 1.7       |

| T-FF          | 8 - 50 GHz                                                                    | 0.8          | 1.1       |

| 4-bit MUX     | 7 - 50 Gbit/s<br>P.M.: 170 deg. for 12.5-G input                              | 1.0          | 1.7       |

| 4-bit DEMUX   | 4 - 50 Gbit/s<br>Sens.:235 mV, P.M.:234 deg.@50G                              | 0.53         | 1.4       |

Sens.: Input Sensitivity P.M.: Phase Margin

Fig. 2. 100-Gbit/s InP HEMT 2-bit MUX IC.

- (a) Chip photograph (chip size: 2 mm x 2 mm).

- (b) Operating waveform at 100 Gbit/s.

#### B. InP HBT ICs

Table 2 shows NTT's InP HBT technology roadmap. The first-generation HBT (G1) has an emitter width of 2 μm. The  $f_T$  and  $f_{max}$  are around 100 GHz and 150 GHz, respectively, at collector current density of 0.5 mA/ $\mu$ m<sup>2</sup>. The second-generation HBT (G2) has been developed for 40-Gbit/s ICs. It has an emitter width of 1.0  $\mu m$  and a Cdoped base structure to improve reliability. The G2 HBT [14] also has undoped-emitter structure to reduce the power consumption of ICs; it exhibits higher  $f_T$  at lower collector current than the conventional n-doped emitter structure [15]. The typical  $f_T$  and  $f_{max}$  of HBTs are around 150 GHz and over 200 GHz, respectively. The thirdgeneration HBT (G3) is being investigated for full-rate 100-Gbit/s ICs. It has an emitter width of around 0.6 to 0.8  $\mu$ m. To achieve high  $f_T$  and  $f_{max}$  of over 300 GHz, the base and collector layers have been thinned to 30 and 150 nm, respectively. This device has the record  $f_T$  value of 341 GHz [16].

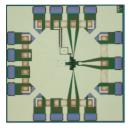

Table 3 summarizes performance of our InP HBT 40-Gbit/s digital ICs using G2 HBTs [17]. A master-slave type D-FF (MS-D-FF), a 4-bit MUX, and a 4-bit DEMUX operate at up to 50 Gbit/s, and a 16-bit MUX also has sufficient speed margin for 40-Gbit/s applications. A full-rate monolithic CDR operates at 40 Gbit/s. To access circuit-level high-speed performance using the G2 HBTs, we designed and fabricated a dynamic 1/8-frequency divider [18] and a selector IC [19]. The dynamic frequency divider operates at 90 GHz and the selector IC operates at 86 Gbit/s. As for G3 devices, we have confirmed 100-GHz operation of a clocked-inverter type dynamic 1/2-frequency divider and 100-Gbit/s operation of a selector IC. Figure 3 shows a

TABLE 2

TECHNOLOGY ROADMAP OF NTT'S INP HBT

| Parameter                 | 1st Generation                        | 2nd Generation                        | 3rd Generation                          |

|---------------------------|---------------------------------------|---------------------------------------|-----------------------------------------|

| Epitaxial Growth          | MOCVD                                 | MOCVD                                 | MOCVD                                   |

| Base Doping               | Zn                                    | С                                     | С                                       |

| Emitter Width             | 2 μm                                  | 1.0 µm                                | 0.8 μm                                  |

| Base Thickness            | 50 nm                                 | 50 nm                                 | 30 nm                                   |

| Doping                    | 4 x 10 <sup>19</sup> cm <sup>-3</sup> | 4 x 10 <sup>19</sup> cm <sup>-3</sup> | 6.0 x 10 <sup>19</sup> cm <sup>-3</sup> |

| Sheet Resistance          | 600 Ω/□                               | 600 Ω/□                               | 600 Ω/□                                 |

| Collector Thickness       | 300 nm                                | 300 nm                                | 150 nm                                  |

| Current Density           | 0.5 mA/μm <sup>2</sup>                | 1.0 mA/μm <sup>2</sup>                | 5.0 mA/μm <sup>2</sup>                  |

| $\mathbf{f}_{\mathrm{T}}$ | $\sim 100 \; GHz$                     | ~ 150 GHz                             | > 300 GHz                               |

| f <sub>max</sub>          | ~ 150 GHz                             | ~ 250 GHz                             | > 300 GHz                               |

TABLE 3

PERFORMANCE OF INP HBT ICS

| Circuit     | Operating Speed                              | Power (W) |

|-------------|----------------------------------------------|-----------|

| D-FF        | 50 Gbit/s                                    | 0.75      |

| CDR         | 40 Gbit/s                                    | 1.7       |

| 4-bit MUX   | 50 Gbit/s<br>P.M.: 180 deg. for 12.5-G input | 2.5       |

| 4-bit DEMUX | 50 Gbit/s<br>P.M.:140 deg.@50G               | 2.6       |

| 16-bit MUX  | 47 Gbit/s                                    | 3.2       |

P.M.: Phase Margin

(a) (b)

Fig. 3. 100-GHz clocked-inverter 1/2 dynamic frequency divider IC.

- (a) Chip photograph (chip size: 1.5 mm x 1.5 mm).

- (b) Output waveform at 100-GHz IC operation.

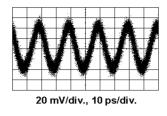

Fig. 4. Output waveform of the 100-Gbit/s InP HBT selector IC.

chip photograph and output waveform of the dynamic frequency divider, while Fig. 4 shows the 100-Gbit/s output waveform of the selector IC. As for a full-rate MS-D-FF, circuit simulations show that the D-FF can operate at 100-Gbit/s.

## IV. PROSPECTS OF 100 GBIT/S AND BEYOND

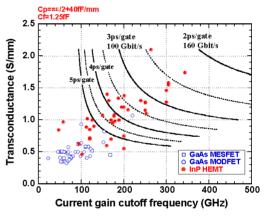

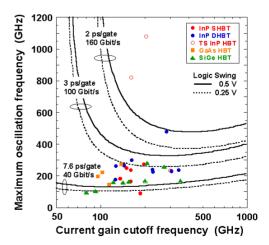

It is important to clarify the transistor performance required for full-rate 100-Gbit/s and 160-Gbit/s circuit operations. Figures 5 and 6 show the propagation delay (tpd) contours of source-coupled FET logic (SCFL) [20] and emitter-coupled logic (ECL) [21], respectively. The performance of state-of-the-art devices is also plotted in these figures. In Fig. 5, it should be noted that the parasitic capacitance is assumed to half that of the stateof-the-art NTT devices. The maximum operating speed of a full-rate MS-D-FF is empirically given by 1/(3.3  $(tpd)^{-1}$  [22]. The delay times should therefore be lower than 3 ps/gate for a 100-Gbit/s MS-D-FF operation and lower than 2 ps/gate for a 160-Gbit/s one. For FET devices, an  $f_T$  of over 280 GHz and a gm of over 1.4 S/mm are needed for 100 Gbit/s, and an  $f_T$  of over 440 GHz and a gm of over 1.9 S/mm are required for 160 Although dynamic circuit configurations like super-dynamic flip-flop [3] relax these requirements, novel device technologies should be developed. satisfy the requirement for 100 Gbit/s, reduction of parasitic capacitance (half that of our current InP HEMT), shortening the gate length (~50 nm) and thinning the barrier layer (~10 nm) are necessary [20]. As for HBT devices, our G3 HBT as well as some other reported HBTs have a potential of achieving 100-Gbit/s D-FF

operation, as shown in Fig. 6. For 160-Gbit/s MS-D-FF operation, an  $f_T$  of around 400 GHz and an  $f_{max}$  of around 500 GHz will be required. To achieve this device performance, emitter width and base and collector thickness should be further scaled down [23].

To construct 100- and 160-Gbit/s transmitters and receivers, we need not only high-speed ICs but also packaging technology covering 100-GHz bandwidth. The need for packaging technology can be alleviated by monolithic integration of optical components and electronic devices. In this case, all functions for receivers and transmitters shown in Fig. 1 should be integrated to make the electrical interface speed lower than the currently available bandwidth (~65 GHz). As for the optical receiver, we have demonstrated a full-rate 40-Gbit/s optoelectronic decision IC [24] integrated with a uni-traveling carrier photodiode [25] and the 0.1-umgate-length InP HEMTs. The photodiode has over 100-GHz-class bandwidth and high-saturation output power. The fusion of high-speed optical device and functional ICs will be the key for beyond 100-Gbit/s.

Fig. 5. Propagation delay contours of SCFL inverters.

Fig. 6. Propagation delay contours of ECL inverters.

# V. CONCLUSION

We reviewed our InP-based IC technologies for optical communications systems. 40-Gbit/s ICs have been developed using the 0.1-μm-gate-length InP HEMT technology. A selector and D-FF using the InP HEMT operate at 100 Gbit/s, which indicates that this HEMT

technology has a potential to construct 100-Gbit/s half-rate clock systems. A 1.0-µm-emitter-width InP SHBT technology has also been developed for 40-Gbit/s MSI-class low-power digital ICs. The next-generation 0.8-µm-emitter-width InP DHBT is being investigated for future full-rate 100-Gbit/s class ICs. InP-based optoelectronic IC technology will play an important role in overcoming the bottleneck of electrical interconnection.

#### ACKNOWLEDGEMENT

The authors thank M. Muraguchi, T. Shibata, Y. Yamane, T. Kobayashi, and K. Komatsu for direction and encouragement throughout this work. They also thank K. Sano, H. Fukuyama, S. Tsunashima, K. Ishii, H. Nosaka, H. Kitabayashi, S. Sugitani, H. Matsuzaki, M. Ida, K. Kurishima, H. Yokoyama, N. Watanabe, Y. Miyamoto, and A. Hirano for fruitful discussions.

#### REFERENCES

- [1] "Network Node Interface for the Synchronous Digital Hierarchy," ITU-T Recommendation G.707, 2000.

- [2] "Interface for Optical Transport Network (OTN)," ITU-T recommendation G.709, 2001.

- [3] T. Otsuji, K. Murata, K. Narahara, K. Sano, E. Sano, and K. Yamasaki, "20-40-Gbit/s-class GaAs MESFET Digital ICs for Future Optical Fiber Communications Systems," *International Journal of High Speed Electronics and Systems*, vol. 9, no. 2, pp. 399 - 435, 1998.

- [4] S. Kimura, Y. Imai, Y. Umeda, and T. Enoki, "Loss-Compensated Distributed Baseband Amplifier IC's for Optical Transmission Systems," *IEEE Trans. on Microwave Theory and Techniques*, vol. 44, no. 10, pp. 1688 1693, 1996.

- [5] S. Masuda, K. Kobayashi, H. Kira, M. Kitajima, M. Takesue, Y. Kamiya, and K. Joshin, "A 100-GHz Distributed Amplifier in Chip-size Package," in Proceedings of IEEE MTT-S IMS, 2003, pp. 1029 1032.

- [6] M. Mokhtari, C. Fields, R. D. Rajavel, "100+ GHz Static Divide-By-2 Circuit in InP-DHBT Technology," in Proceedings of IEEE GaAs IC Symposium, 2002, pp. 291-293.

- [7] K. Murata, K. Sano, H. Kitabayashi, S. Sugitani, H. Sugahara, and T. Enoki, "100-Gbit/s Logic IC using 0.1-μm-gate-length InAlAs/InGaAs/InP HEMTs," in Proceedings of IEEE International Electron Devices Meeting, 2002, pp. 937 939.

- [8] T. Suzuki, Y. Nakasha, T. Sakoda, K. Sawada, T. Takahashi, K. Makiyama, T. Hirose, and M. Takigawa, "A 100-Gbit/s 2:1 Multiplexer in InP HEMT Technology," in Proceedings of IEEE MTT-S IMS, 2003, pp. 1173 1076.

- [9] Y. Baeyens, C. Dorschky, N. Weimann, Q. Lee, R. Kopf, G. Georgiou, J. P. Mattia, R. Hamm, and Y. K. Chen, "Compact InP-Based HBT VCOs with a Wide Tuning Range at W- and D-Band," *IEEE Trans. on Microwave Theory and Techniques*, vol. 48, no. 12, pp. 2403 – 2408, 2000.

- [10] Y. Baeyens and Y. K. Chen, "A monolithic integrated 150 GHz SiGe HBT Push-Push VCO with simultaneous differential V-band output," in Proceedings of IEEE MTT-S IMS, 2003, pp. 877 – 880.

- [11] T. Enoki, H. Yokoyama, Y. Umeda, and T. Otsuji, "Ultrhigh-Speed Integrated Circuit Using InP-Based

- HEMTs," Jpn. J. Appl. Phys.1, vol. 37, no. 3B, pp. 1359 1364, 1998.

- [12] K. Murata, K. Sano, H. Sugahara, and T. Enoki, "Ultrahigh-speed IC and OEIC technologies beyond 40 Gbit/s," in Proceedings of 28th European Conference on Optical Communication, 2002, 9.5.2.

- [13] Y. K. Fukai, S. Sugitani, T. Enoki, H. Kitabayashi, T. Makimura, Y. Yamane, and M. Muraguchi, "Bias Acceleration Model of Drain Resistance Degradation in InP-Based HEMTs," in Proceedings of 2003 International Reliability Physics Symposium, 2003, 4C.3.

- [14] M. Ida, K. Kurishima, N. Watanabe, and S. Yamahata, "Undoped-emitter InP/InGaAs HBTs for high-speed and low-power applications," in Proceedings of International Electron Devices Meeting, 2000, pp. 854 – 856.

- [15] S. Yamahata, H. Nakajima, M. Ida, H. Niiyama, N. Watanabe, E. Sano, and Y. Ishii, "Reliable Carbon-Doped InP/InGaAs HBTs Technology for Low-Power 40-GHz Static Frequency Divider," in Proceedings of International Conference on Solid State Devices and Materials, 1999, pp. 570 571.

- [16] M. Ida, K. Kurishima, N. Watanabe, and T. Enoki, "InP/InGaAs DHBTs with 341-GHz f<sub>T</sub> at high current density of over 800 kA/cm<sup>2</sup>," in Proceedings of International Electron Devices Meeting, 2001, pp. 776 – 779

- [17] T. Shibata, K. Ishii, H. Kamitsuna, and H. Nosaka, "Recent Advances in InP HBT ICs for Future Photonic Networks," in Proceedings of Korea-Japan Joint Workshop on Microwave Photonics, 2003, pp. 29 – 32.

- [18] S. Tsunashima, H. Nakajima, E. Sano, M. Ida, K. Kurishima, N. Watanabe, T. Enoki, and H. Sugahara, "90-GHz operation of a novel dynamic frequency divider using InP/InGaAs HBTs," in Proceedings of 14th Indium Phosphide and Related Materials Conference, 2002, pp. 43 46.

- [19] K. Ishii, K. Murata, M. Ida, K. Kurishima, T. Enoki, T. Shibata, and E. Sano, "Very-high-speed selector IC using InP/InGaAs heterojunction bipolar transistor," *IEE Electron. Lett.*, vol. 38, no. 10, pp. 480 481, 2002.

- [20] T. Enoki, "InP-based HEMT Technologies Toward 100 Gbit/s ICs," in Proceedings of 14th Indium Phosphide and Related Materials Conference, 2002, pp. 439 – 442.

- [21] E. Sano, Y. Matsuoka, and T. Ishibashi, "Device Figure-of-Merits for High-Speed Digital ICs and Broadband Amplifiers," *IEICE Trans. on Electron.*, vol. E78-C, no. 9, pp. 1182 1188, 1995.

- [22] T. Enoki, E. Sano, and T. Ishibashi, "Prospects of InP-based IC Technologies for 100-Gbit/s-Class Lightwave Communications Systems," *International J. of High Speed Electronics and Systems*, vol. 11, no. 1, pp. 137 158, 2001.

- [23] M. J. Rodwell, M. Urteaga, M. Dahlström, S. Krishnan, Z. Griffith, Y. Wei, D. Scott, N. Parthasarathy, Y-M. Kim, and S. Lee, "50-200 GHz InP HBT Integrated Circuits for Optical Fiber and mm-Wave Communications," in Proceedings of 28th European Conference on Optical Communication, 2002, 9.5.1.

- [24] K. Murata, H. Kitabayashi, N. Shimizu, S. Kimura, T. Furuta, N. Watanabe, and E. Sano," A 40-Gbit/s monolithic digital OEIC module composed of unitraveling-carrier photodiode and InP HEMT decision circuit," in Proceedings of IEEE MTT-S IMS, 2000, pp. 345 348.

- [25] T. Ishibashi, N. Shimizu, S. Kodama, H. Ito, T. Nagatsuma, and T. Furuta, "Unit-traveling-carrier photodiodes," *in Proceedings of Ultrafast Electronics and Optoelectronics*, 1997, pp. 166 168.