# A GaAs-HBT Broadband Amplifier with Near-f<sub>T</sub> Cut-off Frequency for High-Bitrate Transmission

Chafik Meliani, Matthias Rudolph, Jochen Hilsenbeck, and Wolfgang Heinrich

Ferdinand-Braun-Institut für Hoechstfrequenztechnik (FBH), 12489 Berlin / Germany Email: meliani@fbh-berlin.de

Abstract — A broadband amplifier for high-bitrate transmission is presented, using a standard GaAs-HBT process with  $f_T$  and  $f_{max}$  of 36 and 170 GHz, respectively, at the operating bias point. The design takes optimum advantage of the available technology, reaching 75% of  $f_T$ , a record value for GaAs HBT. Well-opened output eye diagrams at 20 and 40 Gbps are obtained with 1.4 Vpp and 1.2 Vpp, respectively, as well as a 4 Vpp output swing at 20 Gbps for 1.7 Vpp input signal. The measured eye diagrams demonstrate the potential for applications as 40 Gbps pre-amplifier and 20 Gbps modulator drivers.

## I. INTRODUCTION

In optical communication systems, the targets for amplifier development and realization are twofold: On the one hand, to achieve higher bit rates and improved eyediagram quality for systems at 40 Gbps, and, on the other hand, to accomplish this at lower cost. Thus, the use of low-cost technologies is a very important aspect for the design of transmission-systems building blocks such as broadband amplifiers.

40 Gbps amplification has already been obtained using very high  $f_T$  and  $f_{max}$  technologies such as GaAs pHEMTs [1], or those still under development as the InP HEMT [2]. Moreover, interesting results using CMOS or SiGe have already been reported [3, 4]. Despite their high cut-off frequencies, however, the Si technologies still cannot provide high output voltages. A further choice, not suffering from these limitations, is GaAs-based HBT technology. However, in order to achieve the necessary high  $f_T$  values, significant enhancements in the process were necessary compared to common standard HBT technology, such as selective regrowth of the extrinsic base layer [5].

The work presented in this paper demonstrates feasibility of broadband amplifiers using a standard GaAs-HBT technology for 20 Gbps high-voltage and for 40 Gbps pre-amplifier applications. Since our HBT technology provides extremely high  $f_{max}$  values, we were able to achieve 27 GHz cutoff frequency with HBTs that have an  $f_T$  of only 36 GHz at the relevant bias point. This  $f_e$ -to- $f_T$  ratio of 75% is, to the authors' knowledge, the

highest ratio reported so far for GaAs-based HBTs, while keeping the capability to operate at high output voltages.

The paper is organized as follows. In Section II, the FBH GaAs-HBT process is presented. In Section III, we describe the HBT CAD model and discuss circuit design, with special emphasis on the coplanar environment. Finally, the experimental results are presented and discussed in Section IV.

#### II. TECHNOLOGY

The HBT MMICs are fabricated on the FBH 4" process line using stepper lithography. The epitaxial layers are grown by Metalorganic Vapor-Phase Epitaxy (MOVPE). For further details see [6]. Excessively high  $f_{max}$  values (>170 GHz at  $V_{CE}$  =3 V) are achieved compared to the industry-standard  $f_T$  values (36 GHz at  $V_{CE}$  =3 V). While  $f_T$  is mainly determined by the layer structure,  $f_{max}$  can be increased by optimizing the process. In our case, mainly base resistance R<sub>B</sub> and base-collector capacitance C<sub>bc</sub> are modified. R<sub>B</sub> is reduced by smaller under-etching of the emitter metal, which is used as an etch mask, in order to decrease the distance between emitter and base metalization. He<sup>+</sup>-implantation is applied for deviceisolation. In order to reduce the extrinsic base-collector capacitance C<sub>bc-ex</sub>, we introduce an additional He<sup>+</sup>implantation in the outer region of the base fingers. As a result, the base layer below and the upper part of the collector (approx. 800 nm) become insulating, which strongly decreases C<sub>bc-ex</sub>. Together with a reduction of the base-emitter distance from 1.3  $\mu m$  to 0.5  $\mu m,$  these process optimizations increased  $f_{\text{max}}$  from 95 GHz to 170 GHz.

#### **III. CIRCUIT DESIGN**

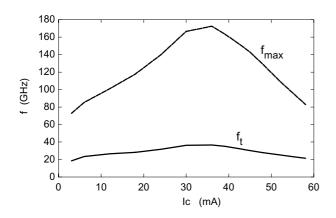

Customized libraries containing both passive and active devices are used for circuit simulation. The FBH HBT model [7,8] is employed. It includes partition of intrinsic and extrinsic base-collector diode, non-ideal base currents, self-heating, base-emitter and base-collector break-down, current-dependence of base-collector capacitance  $C_{bc,intr}$ , and collector transit time  $\tau_c$  (i.e., velocity modulation and Kirk effect, which are responsible for the  $f_T$  and  $f_{max}$  peaking to be seen in Fig. 1).

Fig. 1. Extracted values of  $f_T$  and  $f_{max}$  against collector current for 3x30  $\mu$ m<sup>2</sup> HBT at V<sub>CE</sub>=3 V.

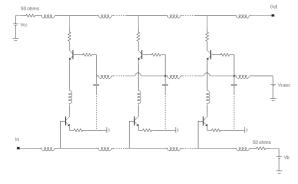

The circuit schematics is shown in Fig. 2. It consists of a five cascode-cell distributed amplifier. This topology provides wide bandwidth and good isolation by canceling the Miller effect.

Fig. 2 Schematic diagram of the distributed amplifier (the actual circuit consists of a total of 5 cells).

Artificial transmission lines are formed using the input or output active device capacitances and the corresponding coplanar line sections for the inductive part. They are designed to have an overall characteristic impedance of 50 ohms. In order to get a flat broadband gain, a feedback resistor is added at the emitter of the first transistor in each cascode cell. Also, the decoupling of the second cascode base represents a key condition for high-frequency operation. In our design, the base is locally decoupled with a series dump resistor of a few ohms and a 5 pF capacitor to the nearest emitter, and is then connected to a longer DC bias line. The diagram of the circuit is shown in Fig. 2.

The collector line is terminated by a 50 ohms load, which is designed in such a way that it provides the DC bias power without significant thermal effects. The backward waves on the input transmission line are absorbed in the 50 ohms resistor, which also feeds the transistors' base bias. The ground areas are interconnected along the transmission lines and around discontinuities to suppress parasitic modes and to ensure correct ground-current flowing paths.

Two main problems exist for broadband-amplifier design: the gain-frequency slope and the gain ripple.

The first one is mainly solved by the unit-cell design: due to the very high HBT gain at low frequencies, an emitter feedback resistor was added to improve the flat broadband behavior.

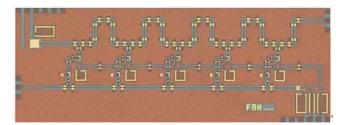

In addition to this, the interconnection between the twocell transistors serves to create a peaking around  $f_c$  to slightly increase the high frequency gain. Because the real part of the HBT output impedance can become negative at high frequencies, dump resistors are added on the transmission lines to lower the reflection coefficients of the amplifying cells and to increase their stability. Main parasitic phenomena such as crossing capacitances and line inductances are checked by em-simulations and included in the design. Fig. 3 presents the chip photo.

The second problem, the gain ripple, was solved by carefully optimizing the coplanar transmission lines for good matching. Because input and output parasitic capacitances of the transistors may differ, equalizing the group delay can require input and output lines to have different lengths.

Fig. 3. Chip photo (size is  $3.6 \times 1.3 \text{ mm}^2$ ).

The operating bias point is chosen as a trade-off between large-signal swing and high values of  $f_T$  and  $f_{max}$ . The small signal  $V_{ce}$  bias is at approximately 3 V, with  $I_c=40$  mA.

### IV. EXPERIMENTAL RESULTS

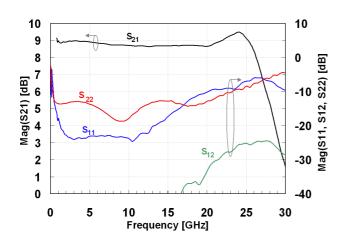

On-wafer measurements show 9 dB broadband gain with a 1 dB in-band ripple. The -3dB cut-off-frequency reaches 27 GHz. DC consumption of the circuit is about 1400 mW for 100 mA DC current. Thus, around 30 % of the global DC voltage drop are in the collector-bias resistance. Important power savings could be achieved by the use of active loads.

Fig. 4. Measured S parameters of the amplifier.

Input and output matching is better than 5 dB within the bandwidth. Under these measurement conditions, the  $f_T$  of the transistor was 36 GHz. Thus, the -3dB cut-off frequency of the amplifier reaches 75 % of  $f_T$ , which is a promising high value. This is mainly attributed to the exceptionally large ratio between  $f_{max}$  and  $f_T$ .

The large-signal behavior was tested with a  $2^{31}$ -1 PRBS NRZ bit pattern provided by a 2:1 multiplexer. An attenuator was needed between the MUX and the amplifier so that the input signal swing reached approximately 500 mVpp.

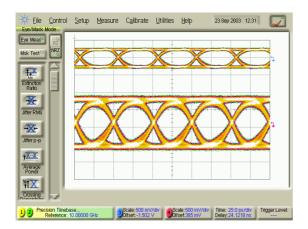

Fig. 5 shows the measured input and output accumulated eye diagrams at 20 Gbps. The circuit delivers output signal amplitude of 1.4 Vpp, at a large-signal gain of approximately 8.9 dB. The amplifier is still operating in a linear region since no gain compression is observed.

Fig. 5. 20 Gbps input (top) and output (bottom) eye diagrams.

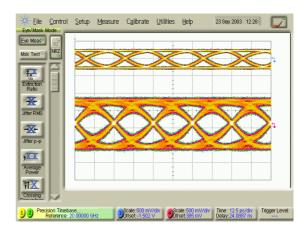

Fig. 6 presents the circuit eye diagrams at 40 Gbps. The amplifier operates correctly and for the same input signal amplitude. The output signal swing reaches 1.2 Vpp, at a large-signal gain of 7.6 dB. The slightly lower gain value, compared to 20 Gbps, is due to the lack of gain at high frequencies and not to any compression phenomena. Because of the shape of its spectra, the major part of the energy of a NRZ signal is contained in its first lobe. This explains that a correctly opened eye diagram at 40 Gbps can be obtained with a -3dB cut-off-frequency  $f_c$  of 27 GHz. Of course, increasing  $f_c$  would increase the higher frequency components, which improves the waveform and, consequently, the bit-error rate.

Fig. 6. 40 Gbps input (top) and output (bottom) eye diagrams.

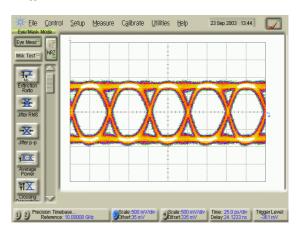

In order to check large-signal performance, the maximum available signal of the MUX at 20 Gbps  $(1.7 V_{pp})$  was applied to the amplifier (see Fig. 7).

Fig. 7. 20 Gbps input signal eye diagrams.

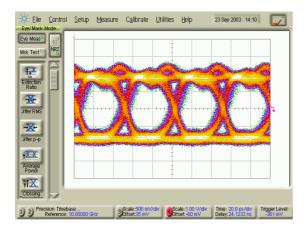

The eye diagram of the corresponding output signal is shown in Fig. 8. The signal has a 4 Vpp amplitude. The large signal gain is 7.5 dB.

Fig. 8. 20 Gbps output signal eye diagrams.

#### **IV. CONCLUSIONS**

A broadband amplifier suitable for high bit-rate communications using a standard GaAs HBT technology with  $f_T/f_{max}$  of 36/170 GHz is presented. Measured results demonstrate baseband operation with a -3dB cut-off-frequency of 27 GHz, and a very flat small-signal gain of 9 dB. To our knowledge, this is the highest  $f_c/f_T$  ratio ever reported for a GaAs HBT technology. Output voltage swings up to 4 Vpp at 50  $\Omega$  are achieved. Regarding high bit-rate long-haul optical transmission systems, the measured eye diagrams of the amplifier show very interesting and promising results for application in 40 Gbps pre-amplifiers and 20 Gbps modulator drivers.

#### **ACKNOWLEDGEMENTS**

The authors are grateful to M. Ludwig and Dr. M. Schlechtweg of the Fraunhofer Institute IAF, Freiburg, for performing the eye-diagram measurements, and to S. Schulz of FBH for performing the S-parameter measurements. This work is supported by the German BMBF under contract No. 01BP285.

#### REFERENCES

- H. Shigematsu, M. Sato, T. Hirose, Y. Watanabe, "A 54-GHz distributed amplifier with 6-V/sub PP/ output for a 40-Gb/s LiNbO/sub 3/ modulator driver," *IEEE Journal of Solid-State Circuits*, Vol. 37, 1100–1105, Sep 2002.

- [2] S. Masuda, T. Hirose, T. Takahashi, M. Nishi, S. Yokokawa, S. Iijima, K. Ono, N. Hara, K. Joshin, "An over 110-GHz InP HEMT flip-chip distributed baseband amplifier with

inverted microstrip line structure for optical transmission systems", *Gallium Arsenide Integrated Circuit (GaAs IC) Symposium*, Monterey, CA, 2002.

- [3] Hee-Tae Ahn, and David J. Allstot, "A 0.5–8.5-GHz Fully Differential CMOS Distributed Amplifier," *IEEE Journal of Solid-State Circuits*, Vol. 37, Aug. 2002.

- [4] O. Wohlgemuth, P. Paschke, and Y. Baeyens, "SiGe broadband amplifiers with up to 80 GHz bandwidth for optical applications at 43 Gbit/s and beyond", *European Microwave Conference* - Munich 2003, pp. 1087-1090.

- [5] Y. Amamiya, Y. Suzuki, M. Kawanaka, K. Hosoya, Z. Yamazaki, M. Mamada, H. Takahashi, S. Wada, T. Kato, Y. Ikenaga, S. Tanaka, T. Takeuchi, H. Hida "40-Gb/s optical receiver IC chipset - including a transimpedance amplifier, a differential applier, and a decision circuit – using GaAs-based HBT technology", in: 2002 IEEE MTT-S Int. Microwave Symp. Dig., vol. 2, pp. 87-90, June 2002

- [6] H. Kuhnert, F. Lenk, J. Hilsenbeck, J. Würfl, W. Heinrich, "Low Phase-Noise GaInP/GaAs-HBT MMIC Oscillators up to 36 GHz," 2001 IEEE MTT-S Int. Microwave Symp. Dig., vol. 3, pp. 1551-1554, June 2001.

- [7] M. Rudolph, R. Doerner, K. Beilenhoff, P. Heymann, "Scalable GaInP/GaAs HBT Large-Signal Model", *IEEE Trans. Microwave Theory Tech.*, vol. 48, 2370 – 2376, Dec. 2000.

- [8] M. Rudolph, R. Doerner, K. Beilenhoff, P. Heymann, "Unified Model for Collector Charge in Heterojunction Bipolar Transistors," *IEEE Trans. Microwave Theory Tech.*, vol. 50, 1747 – 1751, July 2002.