# **Characterization of an ASIC Front-End electronics dedicated**

## to Silicon Drift Detectors

C. Labanti<sup>1</sup>, G. Baldazzi<sup>2,3</sup>, P. Malcovati<sup>4</sup>, G. Bertuccio<sup>5</sup>, M. Feroci<sup>6,7</sup>, R. Campana<sup>6,7</sup>, M. Grassi<sup>4</sup>, L. Picolli<sup>4</sup>, E. Del Monte<sup>6,7</sup>, L. Pacciani<sup>6,7</sup>, Y. Evangelista<sup>6,7</sup>, F. Muleri<sup>6</sup>, E. Costa<sup>6</sup>, I. Donnarumma<sup>6</sup>, F. Lazzarotto<sup>6</sup>, F. M. Rapisarda<sup>6,7,8</sup>, A. Rubini<sup>6,7</sup>, P. Soffitta<sup>6</sup>, M. Mastropietro<sup>6</sup>, M. Marisaldi<sup>1</sup>, E. Morelli<sup>1</sup>, A. Vacchi<sup>9</sup>, G. Zampa<sup>9</sup>, V. Bonvicini<sup>9</sup>, A. Rashevsky<sup>9</sup>, N. Zampa<sup>9</sup>, A. Battistella<sup>10</sup>, M. Bello<sup>10</sup>, C. L. Fontana<sup>11</sup>, N. Uzunov<sup>10,13</sup>, F. Navarria<sup>2,3</sup>, M. Zuffa<sup>3</sup>, P. Rossi<sup>11,12</sup>, G. Moschini<sup>11,12</sup>

{<sup>1</sup>INAF/IASF-Bologna, <sup>2</sup>Università di Bologna, Dip. di Fisica, <sup>3</sup>INFN Sezione di Bologna, <sup>4</sup>Università di Pavia, Dip. di Ingegneria Elettrica, <sup>5</sup>Politecnico di Milano, Dip. di Ingegneria Elettrica, <sup>6</sup>INAF/IASF-Roma, <sup>7</sup>INFN - Sezione di Roma 2, <sup>8</sup>ENEA Frascati, <sup>9</sup>INFN - Sezione di Trieste, <sup>10</sup> Laboratori Nazionali di Legnaro, INFN Legnaro (Padova), <sup>11</sup>Università di Padova, Dipartimento di Fisica, <sup>12</sup>INFN - Sezione di Padova}: Italy <sup>13</sup> Faculty of Natural Sciences, Shumen University, Bulgaria

#### **The Context**

# Large-area multi-anode Silicon Drift Detectors (SDDs) have X-ray imaging and spectroscopic characteristics that make them extremely attractive in the perspective of their applications to the field of space astrophysics and in instruments for medical diagnostic imaging.

We describe here the activity aimed to develop an ASIC suitable for coupling with SDDs.

The ASIC described here is the first prototype of front end electronics to be used for the readout of largearea SDD of a similar design of that one developed for the Inner Tracking System (ITS) in the ALICE experiment of the Large Hadron Collider (LHC) at CERN.

#### **ASIC Main Features**

| FUNCTION                                          | IMPLEMENTATION                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input: Readout of 32 SDD anodes                   | 32 parallel inputs channels, current input<br>Channel pitch 200 μm                                                                                                                                                                                                                                           |

| Pre-amp                                           | DC coupling<br>Input range 120 – 12000 e <sup>-</sup><br>Detector param. 150 pA max leak curr, 0.5 pF max                                                                                                                                                                                                    |

| Signal processing<br>32 Read-out Pixel Cell (RPC) | Low-noise preamplifier<br>Pulse shaper CR-RC <sup>2</sup> with pole zero suppression,<br>Amplitude discriminator<br>Peak discriminator and stretcher<br>Digital circuits required for cell operation                                                                                                         |

| Commanding<br>configuring the internal registers  | <ul> <li>Shaping time (selectable from 0.5 to 10 µsec)</li> <li>Discriminator level (general + individual tuning of the ch)</li> <li>Channel disabling (of both pre-amp and discriminator)</li> <li>External trigger (selectable)</li> <li>Output mode: shaper or stretched output in selected ch</li> </ul> |

| Output                                            | Internal trigger (OR of all channel trigger)<br>Analogue output (parallel) for ch from #15 to #22<br>Analogue output (serial) of stretched signals after a MUX                                                                                                                                               |

These detectors can reach large area of some tenth of cm<sup>2</sup> with anode pitch of various size from some hundred of micrometer so a millimeter, and can be used with very good spectroscopic capabilities for low energy X-ray detection.

Similar detector with their electronic readout can find application in many different mission ranging from configuration devoted to X-ray spectroscopy, imaging or timing observation to configuration conceived for gamma-ray observation like for example in architectures at the base of a Compton telescope design.

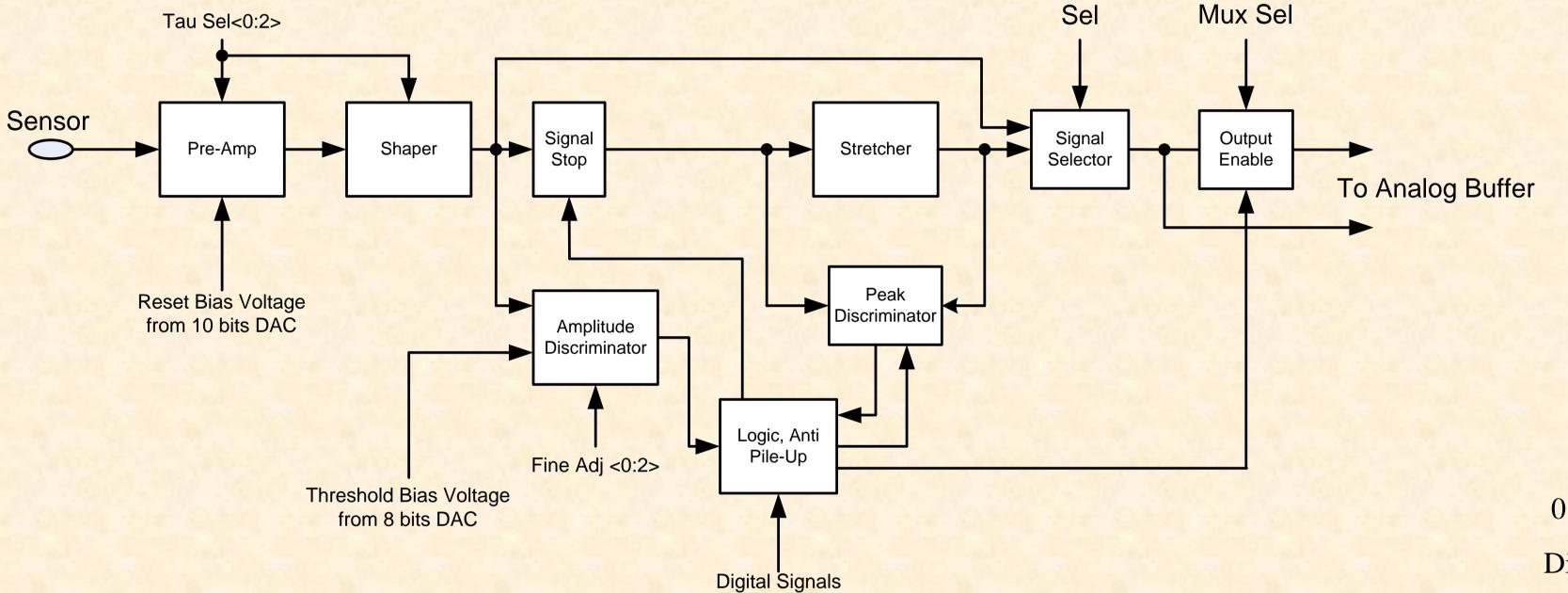

#### **One channel simplified architecture**

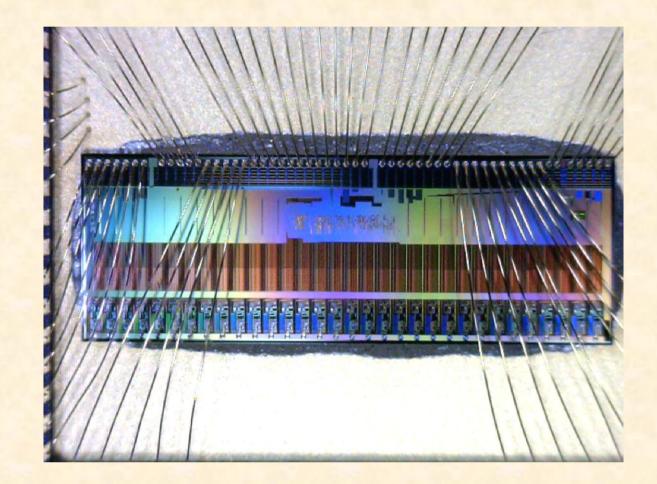

The ASIC in its packaged version

0.35 mm CMOS technology

The first ASIC prototype design

**Read-Out Channels**

Dutput Buffers and DACs

Analog Pads

Die dimension are  $6.4 \times 2.3$  mm channel pitch 200  $\mu$ m

**Digital Pads**

Programmable Registe

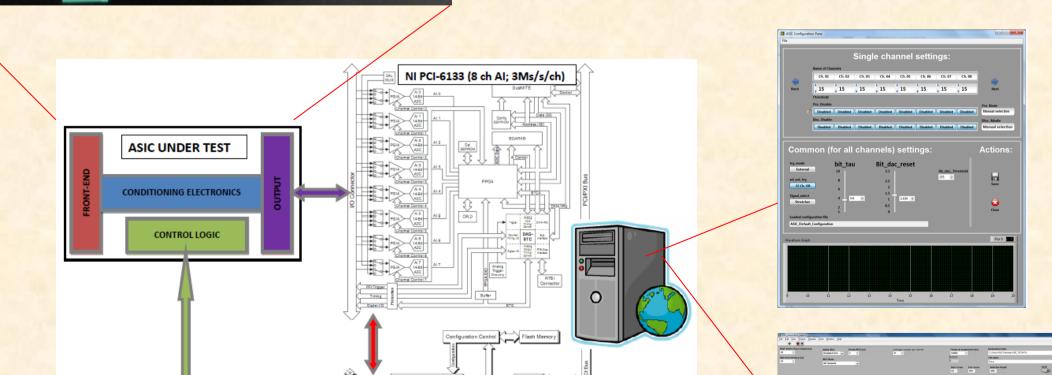

### The testing system

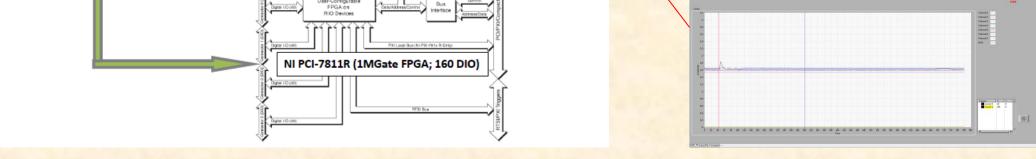

The ASIC testing system consist of two PC boards: the first one with digital input/output for ASIC configuration and commanding, the second one for ASIC commanding during operation and for ADC conversion.

Different graphical interfaces are used for choosing ASIC configuration, data acquisition and visualisation

Prototype board with the ASIC bonded to a multi-anode SDD.

### **Read out sequence for a detected event**

Analog Pads

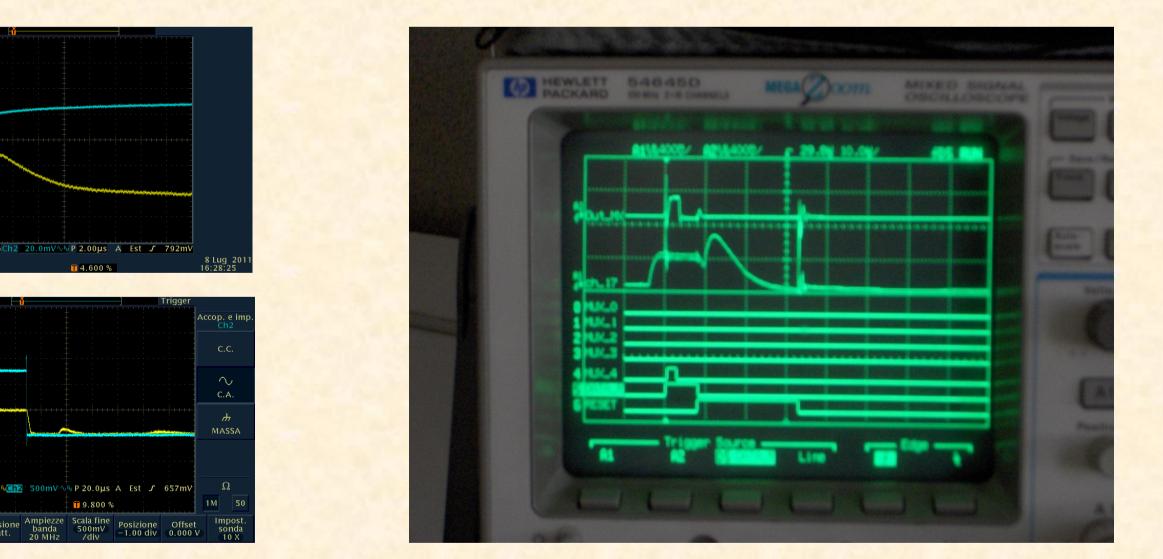

ASIC functionality on ch #15 (ch #15 chain ON (shaping 1 µsec), all other channels OFF)

Left: Output of the channel chain from the tes\_pin of the channel (available only for ch from #15 to #22 will be removed in final design). Top ASIC in shaping configuration, bottom ASIC in stretching configuration, in both cases internal trigger is used.

| Right: Output from the MUX pin (internal trigger is used); signal sequence from top to bottom |  |

|-----------------------------------------------------------------------------------------------|--|

| Analog                                                                                        |  |

| Analog                                                                                        |  |

| Digital (5 bits)                                                                              |  |

| Digital (must be long enough to allow multplexing operations)                                 |  |

| Digital                                                                                       |  |

|                                                                                               |  |

The functional behaviour of the ASIC is correct; the performance figure of the ASIC are still under test, expectation from circuit simulation are that the noise figure is contained in some tent of e- rms, with a power consumption of about 1 mW/ch

A new ASIC run is foreseen in the next months

Schematics of the ASIC Test Equipment.

Graphical interfaces of the Test Equipment for ASIC configuration and real time signals display