# A InGaP/GaAs HBT WLAN Power Amplifier with Power Detector

Kyung Ai Lee, Dong Ho Lee, and Hyun-Min Park, Sang-Hoon Cheon<sup>1</sup>, Jae-Woo Park<sup>1</sup>, Hyung-mo Yoo<sup>2</sup> and Songcheol Hong

Dept. EECS, KAIST 373-1, Guseong-dong, Yuseong-gu, Daejeon, 305-701, Republic of Korea

<sup>1</sup>Knowledge.on Inc., 513-37, Eoyang-dong, Iksan, 570-210, Republic of Korea

<sup>2</sup>Dynalinear Technologies, Inc. 2860 Zanker Road, Suite 206 San Jose, CA95134

Abstract —A two-stage InGaP/GaAs heterojunction bipolar transistor (HBT) power amplifier is developed for WLAN 802.11b application. This is integrated with power detector that senses input power of power stage in order to decrease output power loss of detecting. The power amplifier delivers up to 26dBm output power with the maximum power-added efficiency (PAE) of 31% including consumption of the power detector under the supply voltage of 3.3V

#### I. INTRODUCTION

In wireless systems, the power amplifier (PA) is one of the highest energy-consuming components. The efficiency of the power amplifier is the key requirement [1]. To improve power added efficiency (PAE), an RF power amplifier can be operated in high efficient modes such as class-B, class-E, and class-F. However, these high efficiency amplifiers have nonlinearity, which result in unacceptable adjacent channel power ratio. In order to satisfy the linearity requirement, power amplifiers are typically operated in linear Class-A or Class-AB configurations [2]. But these power amplifiers have low power efficiency. The gain should be increased to improve PAE in the same supply voltage. To increase the overall power amplifier gain, the number of stages in PA must be increased. This increases the chip size, as well as idle bias currents. If the gain of each stage power transistor is quite high, two-stage configuration achieves the enough gain. A method to increase gain in a power transistor is to use a split R/C ballasting power transistor [3]. A power detector to measure the RF output power is the key requirement for power control. Usually, output power is monitored at output load, which causes the degradation of output power [4-5].

In this paper, the input power of power stage is sensed, and the power level is indicated by the output voltage of power detector. The two-stage power amplifier, which comprises of high gain power transistors, is presented.

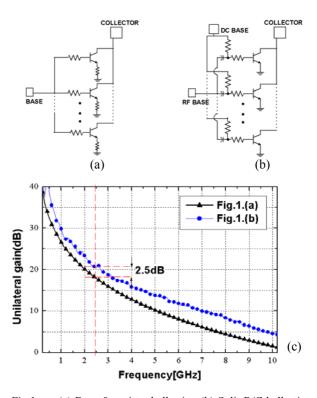

Fig.1. (a) Base & emitter ballasting (b) Split R/C ballasting (c) Measured unilateral gain of two structures at same bias condition. (The emitter size is 1920um<sup>2</sup>)

#### II. DEVICE CHARACTERISTICS

As in Si BJT, HBT exhibits thermal instability-related failures when operated under large dc or RF drive conditions. Thermal instability can be reduced by use of ballast resistors in series with each emitter or base as shown in Fig 1. (a) [6]. But a major problem with this ballast resistance is RF gain degrading. To solve the problem, the power transistor is designed with split R/C ballasting. Fig.1 (b) illustrates the scheme of the split R/C ballasting. The DC ballast resistors have no effect on RF gain performance. This structure shows improvement of

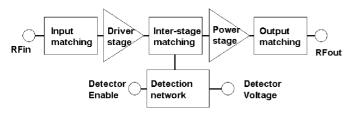

Fig. 2. The topology of the power amplifier with proposed power detector.

about 2.5dB unilateral gain compared with base and emitter ballasting in 2.45GHz at same bias condition as shown in Fig 1. (c). Power transistor is modeled including self-heating and ambient temperature effects [7].

## III. 2-STAGE POWER AMPLIFIER WITH POWER DETECTOR

The topology of the power amplifier with proposed power detector is described in Fig. 2.

#### A. Power detector

So far, power detection by diode and log amp at power stage output is a simple method that detects power delivered to the load [8]. However, these detection methods decrease output power, directly. The output power is related to emitter area of power stage. To get same output power, the power transistor needs the more emitter area.

The power detection at the input of the power stage is good approach to decrease output power loss. Because input power of power stage does not follow power stage output characteristics, the detection amplifier is needed to follow power stage output. A similar structure is seen by [9]. A part of detection is integrated in [9], which needs additional circuits to get power detector voltage. Also, it uses common bias circuit with power stage, power detector is always turned on. Considering detector transistor operation current in detection circuit, detector on/off is needed for not working detection. In this paper, a simple structure is integrated which get power detector voltage and turn on/off the power detection.

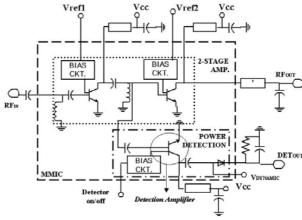

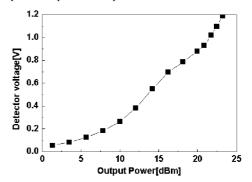

As shown in Fig 3., because the detector amplifier of power detection is designed to follow power stage characteristics, it has some PAE degradation. To get less degradation, the detector amplifier is working in low bias region. It makes input of diode decreased, output detector voltage has low dynamic range. To compensate this effect, diode has  $V_{\rm DYNAMIC}$ . In measurement result, detector voltage of power detector has 0.2 to 1.2V as output power sweep 0 to 24dBm.

Fig. 3. Schematic diagram of the fabrication InGaP/GaAs power amplifier with power detector.

Fig. 4. Measured detector voltage

#### B. Power amplifier

The two-stage power amplifier was implemented with InGaP/GaAs HBT technology. The emitter sizes of the first stage and second stage HBT were  $480 \text{um}^2$  and  $1920 \text{um}^2$ . The detail schematic diagram of the circuit is displayed in Fig. 3. The power amplifier has an integrated input and interstage-matching network. The optimum input and output impedance of the HBTs are determined by large-signal models [7].

Bias circuits are completely on-chip except the collector circuitry of the output stage. This part is off-chip to minimize power loss. The bias current level can be tuned to a desired value by controlling the reference voltage (Vref) in the bias circuit.

#### IV. MEASUREMENT

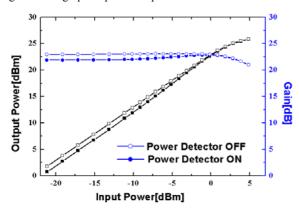

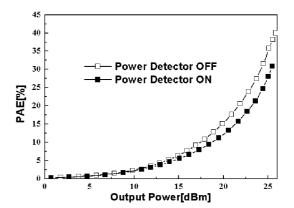

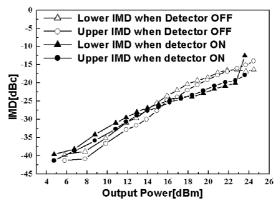

Fig. 5. is photograph of the power amplifier with integrated power detector. The chip size is 1.2mm× 1.0mm. Fig. 6, 7, 8 shows the measured results of the power amplifier at 2.45GHz. The bias current is set to 37mA and 83mA for driver and power stage with a supply voltage of 3.3V.

Fig.5. Photograph of power amplifier

Fig.6. Measured output power and gain of power amplifiers

When power detector is on, power amplifier achieves  $P_{1dB}$  of 26 dBm and a gain 22 dB. The power added efficiency is over 31%.  $P1_{dB}$  is not degraded, as was expected. The gain is degraded about 1dB.IMD is measured as -20 dBc at 24dBm in  $\pm 500 KHz$  offset frequency. In simulation result the IMD is -27 dBc at 24dBm, the difference is presented by in accurate measurement setup.

#### V. CONCLUSIONS

A two-stage InGaP/GaAs HBT power amplifier with integrated power detector for wireless LAN application is presented. The output voltage of power detector indicates the power level. The power amplifier has 31 % PAE at 26 dBm output power with 22 dB gain at 2.4 to 2.5 GHz. Power detector consumes 0.4dB of output power at P1<sub>dB</sub>.

#### ACKNOWLEDGEMENT

This research was supported by University IT Research Center Project.

Fig.7. Measured PAE.

Fig.8. Measured IMD.

### REFERENCES

- [1] T. Yoshimasu, "An HBT MMIC power amplifier with an integrated diode linearizer for low-voltage portable phone applications.", , IEEE Journal of Solid-State Circuits, Volume: 33 Issue: 9, Sept. 1998

- [2] K.Yang, "High-efficiency class-A power amplifiers with a dual-bias-control scheme", IEEE Transactions on Microwave Theory and Techniques, Volume: 47 Issue: 8, Aug. 1999.

- [3] W.P. Pratt. "HBT Power Amplifier," U.S.Patent 5629 648,May 13,1997

- [4] http://www.intersil.com

- [5] http://www.maxim-ic.com

- [6] S.Jeon, "Thermal characteristics of InGaP/GaAs HBT ballasted with extended ledge", IEEE Transactions on Electron Devices, Volume: 48 Issue: 10, Oct. 2001

- [7] H.Park, "A novel temperature-dependent large-signal model of heterojunction bipolar transistor with a unified approach for self-heating and ambient temperature effects", IEEE Transactions on Electron Devices, Volume: 49 Issue: 12, Dec. 2002 p.p. 2099 –2106

- [8] Pollanen, O. "Integrated power measurement circuit for RF power amplifiers." 2000 IEEE Radio and Wireless Conference, RAWCON 10-13 Sept. 2000 p.p235 -238

- [9] RF 5117, http://www.rfmd.com