# A New Empirical Non-linear Model for SOI MOSFET

Alexandre Siligaris, Matthieu Vanmackelberg, Gilles Dambrine, Nicolas Vellas, François Danneville

IEMN, UMR CNRS 8520, Avenue Poincaré, BP 69, 59652 Villeneuve d'ASCQ, France Phone number: 33 (0)3 20 19 78 61, Fax number: 33 (0)3 20 19 78 92, alexandre.siligaris@iemn.univ-lille1.fr

Abstract – An empirical non-linear model for SOI MOSFET useful for large-signal simulations of high frequency circuit design is presented. An original close form expression is proposed for the drain current and charge conservation is taken into account, as capacitances are derived from a single charge model. The model's parameters are first extracted, prior the model implementation in a circuit simulator. Then some comparisons with experimental data are proposed to validate the model. Note that the model is well suited for the Fully Depleted either the Partially Depleted devices.

#### INTRODUCTION

SOI MOSFET devices present more and more interesting high frequency performances along with the continuous decrease of the gate length. For this reason, it seems realistic to use such devices in centimetrique and probably millimetrique wave ranges [1] [3].

Several empirical non-linear models for MESFET's and HEMT's have been developed for high frequency applications, but not so much for MOSFET on SOI substrate. The existing ones are generally physics oriented and they require technological data for their parameter extraction [2].

The aim of this paper is to present an empirical non-linear model for SOI MOSFET, easy to extract, scalable on gate width, for applications like amplifiers, mixers and oscillators down to the millimetrique range. This model which was studied for Fully Depleted (F.D.) and Partially Depleted (P.D.) SOI MOSFET's realised by the CEA LETI [3], describes accurately their electrical (DC-AC) characteristics. It includes a non-linear drain current expression that is continuous and infinitely derivable, leading the transconductance and the drain conductance to be continuous. The capacitances are derived directly from a gate charge expression that ensures the charge conservation principle.

# THE NON LINEAR DRAIN CURRENT

The drain current equation is originally based on the Angelov's [4] model developed for III-V devices, but it has been modified in order to be suitable for SOI devices:

$$I_{dsi}(V_{gsi}, V_{dsi}) = Kf(V_{gsi})f(V_{gsi}, V_{dsi})$$

(1)

In (1), the first function depends on the control voltage  $V_{gsi}$  while the second one is dependent on both  $V_{gsi}$  and  $V_{dsi}$ . More specifically the drain current is given by the following expression:

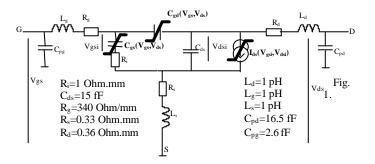

Equivalent-circuit model for the MOS SOI with the non-linear elements. Intrinsic and extrinsic element values for an F.D. SOI MOS with Lg=0.25  $\,$   $\mu m$  and W=8x12.5  $\mu m$ .

$$\begin{split} &I_{ds}(V_{gsi},V_{dsi}) = I_{pk}W_f n_f \left[ \left[ 1 + P(V_{gsi}) \tanh \left( \Psi(V_{gsi}) \right) \right] \times \\ &\times \left[ P(V_{gdi}) \tanh \left( V_{dsi} \left( K_7 V_{gsi} + \mathbf{a} \right) \right] \right] \times \left[ 0.5 \left( 1 + \tanh \left( (V_{gsi} - \frac{V_{th}}{2}) 10^6 \right) \right) \right] \end{aligned} \tag{2} \\ &\Psi(V_{gsi}) = P_1 \left( V_{gsi} - V_{pk} \right) + P_2 \left( V_{gsi} - V_{pk} \right)^2 + P_3 \left( V_{gsi} - V_{pk} \right)^3 \\ &P(V_{gsi}) = K_0 + K_1 V_{gsi} + K_2 V_{gsi}^2 + K_3 V_{gsi}^3 \\ &P(V_{gdi}) = 1 + K_4 V_{gdi} + K_5 V_{gdi}^2 + K_6 V_{gdi}^3 \end{split}$$

In (2) Y is the same term as those used in Angelov model [4]. Polynomial expressions were added to better describe the experimental variations of the transconductance  $g_m$  and conductance  $g_d$  in the saturation regime. The term  $tanh(V_{dsi}(K_7V_{gsi}+a))$  describes the region between the linear and the saturation regime of the transistors. The last term ensures a current to be equal to zero in subthreshold region and for negative gate biases. All the terms  $P_i$ ,  $K_i$ , a,  $V_{pk}$  and  $I_{pk}$  are the current model's parameters,  $W_f$  is the transistor's width per finger and  $n_f$  the number of fingers.  $V_{th}$  is the measured threshold voltage. They don't have any real physical meaning (except of  $V_{th}$ ) even if some of them have physical dimensions.

The transconductance's and conductance's equations are given by:

$$g_{mi}(V_{gsi}, V_{dsi}) = \frac{dI_{ds}}{dV_{gsi}|_{V_{dsi} = cte}}$$

$$g_{di}(V_{gsi}, V_{dsi}) = \frac{dI_{ds}}{dV_{dsi}|_{V_{esi} = cte}}$$

(3)

This model describes the static current versus the intrinsic voltages  $V_{\rm gsi}$  and  $V_{\rm dsi}$  taking into account the potential drop across  $R_s$  and  $R_{\rm d}$ .

## THE NON LINEAR CAPACITANCE

The best way to model capacitance and to keep charge conservation is to consider the total charge at a given physical point of a device [5]. The charge on the gate electrode depends on the gate bias and the drain bias:  $Q_g(V_{gsi}, V_{dsi})$ . The capacitance  $C_{gs}$  and  $C_{gd}$  will be [5]:

$$C_{gs} + C_{gd} = \frac{dQ_g}{dV_{gsi}}$$

$$V_{gsi} \quad C_{gd} = -\frac{dQ_g}{dV_{dsi}}$$

$$V_{gsi} \quad V_{gsi} = cte$$

$$V_{gsi} \quad V_{gsi} = cte$$

$$V_{gsi} \quad V_{gsi} = cte$$

The capacitances  $C_{gs}$  and  $C_{gd}$  are derived from the same charge expression and are interdependent. They have to verify this mathematical relation (4), otherwise the model is not charge conservative. Using a charge model from which the expressions for  $C_{gs}$  and  $C_{gd}$  are calculated by (4), we can model the gate capacitances without having to take into account of a transcapacitance  $C_m$  element [5], [6].

Following this principles the gate charge for the MOS SOI transistors was modelled by the equation inspired by [7]:

$$\begin{split} Q_{g} &= K \Big( f_{1}(V_{gsi}, V_{dsi}) + f_{2}(V_{gsi}, V_{dsi}) \Big) \\ K &= C_{0} n_{f} W_{f} \Big( L_{g} - 2L_{d} \Big) \\ f_{1} &= \Big( C_{gg1} V_{gsi} + C_{gg2} V_{gsi}^{2} + C_{gg3} V_{gsi}^{3} \Bigg[ C_{gg0} + \tanh \left( \frac{V_{dsi}^{2}}{g V_{gsi}^{2}} \right) \Bigg] \end{split}$$

(5)

$$f_{2} &= \Big( C_{gd1} V_{gdi} + C_{gd2} V_{gdi}^{2} \Bigg[ C_{gd0} + \tanh \left( -\frac{V_{dsi}}{V_{t}} \right) \Bigg] \end{split}$$

In (5),  $L_g$  is the gate length,  $W_f$  the gate width per finger and  $n_f$  the number of fingers.  $C_0$ ,  $L_d$ ,  $C_{ggi}$ ,  $C_{gdi}$ , g and  $V_t$  are the model parameters. (4) and (5) give the explicit functions for  $C_{gs}$  and  $C_{gd}$ .

## SIMULATION, RESULTS

We present here the results obtained for a FD SOI MOSFET with  $W=8x12.5~\mu m$ ,  $Lg=0.25~\mu m$  and with salicide gate. The model parameters extracted for this transis tor are summarized in table I.

| TABLE I            |                |           |                |                  |                |                |                |                |           |          |   |       |

|--------------------|----------------|-----------|----------------|------------------|----------------|----------------|----------------|----------------|-----------|----------|---|-------|

| Current parameters |                |           |                |                  |                |                |                |                |           |          |   |       |

| $V_{pk}$           | $I_{pk}$       |           | a              | $\mathbf{P}_{1}$ |                | $\mathbf{P}_2$ |                | P <sub>3</sub> |           | $V_{th}$ |   |       |

| 403.7              | 34.89          |           | 0.808          | 2.434            |                | -0.791         |                | 1.016          |           | 0.34     |   |       |

| m V                | mA/mm          |           | V-1            | V-1              |                | V-2            |                | V-3            |           | V        |   |       |

| $K_0$              | $\mathbf{K}_1$ |           | $\mathbf{K}_2$ | ]                | K <sub>3</sub> |                | K <sub>5</sub> |                | 5         | $K_6$    |   | $K_7$ |

| 1.202              | 2.118          |           | 4.613          |                  | -0.799         |                | 0.049          |                | .049      | 0.06     | 1 | 2.962 |

| _                  | V-1            |           | $V^{-2}$       | ١,               | V-3            |                | V-1            |                | r-2       | V-3      |   | V     |

| Charge parameters  |                |           |                |                  |                |                |                |                |           |          |   |       |

| $C_0$              |                | $L_d$     | $C_{gg0}$      |                  | $C_{gg1}$      |                | $C_{gg2}$      |                | $C_{gg3}$ |          |   |       |

| 1.768              |                | 4.441     | -4.905         |                  | -24.78         | -24.78         |                | -29.63         |           | 6.066    |   |       |

| fF/mm <sup>2</sup> |                | fm        | _              |                  | _              | V-1            |                |                | V-2       |          |   |       |

| $C_{gd0}$          |                | $C_{gd1}$ | $C_{gd2}$      |                  | ?              |                | $V_t$          |                |           |          |   |       |

| 1.671              |                | 51.68     | -17.36         |                  | 0.584          |                | 1.552          |                |           |          |   |       |

| _                  |                | _         | V-1            |                  | _              |                | V              |                |           |          |   |       |

The parameters were extracted using an optimisation procedure in the ICCAP environment (Agilent Technologies EEsof), by adjusting the model equations on the measured DC and AC data. The intrinsic and extrinsic elements were deduced from bias depending S-parameter measurements [8]. The model was implemented in the ADS (Agilent Technologies EEsof) circuit simulator. Small signal and large signal simulations were carried out in order to perform some comparisons with experimental data and validate the model.

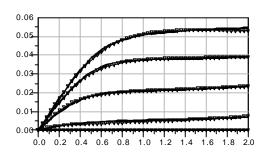

Fig. 2.a Static drain current versus drain bias for 5 different values of gate bias. Measurements (symbols) and model (solid line).

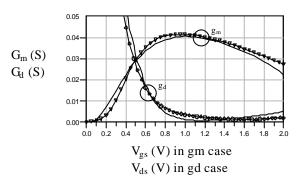

Fig. 2.b Static transconductance gm versus gate bias Vgs for Vds=1V. Measurements (triangles) and model (solid line). Static conductance gd versus drain bias Vds for Vgs=1V. Measurements (circles) and model (solid line).

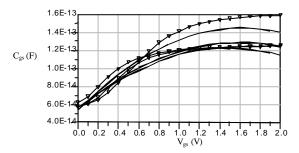

We observe an excellent agreement in Fig.2a-b upon the static simulation for the drain current versus  $V_{ds}$  for different values of  $V_{gs}$ , but also for the output conductance  $g_d$  and the transconductance  $g_m$ . In Fig.3 is shown the capacitance  $C_{gs}$  measured and modelled by the expressions (4) and (5). There is a slight disagreement due to the fact

that, a priori, we don't know the exact expression of the gate charge, nevertheless the model is charge conservative.

Fig. 3. Capacitance Cgs versus gate bias Vgs for Vds=0, 1 and 2 V. Measurements (symbols) and model (solid line).

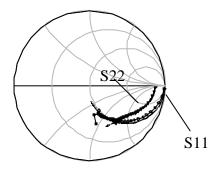

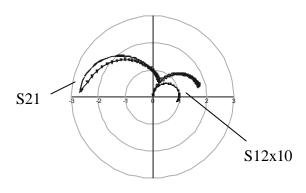

Next, in Fig.4 a-b, the small-signal simulations are compared to the measured ones. The four S-parameters are plotted for frequencies varying from 0.25 GHz to 50 GHz and the agreement is quite good.

Fig. 4.a S11 and S22 parameters versus frequency varying from 0.25 GHz to 50 GHz for Vgs=0.6 V and Vds=1 V. Measurements (symbols) and model (solid line).

Fig. 4.b S21 and S12(x10) parameters versus frequency varying from 0.25 GHz to 50 GHz for Vgs=0.6 V and Vds=1 V.

Measurements (symbols) and model (solid line).

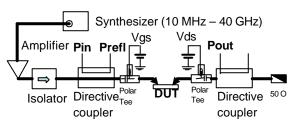

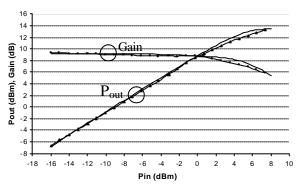

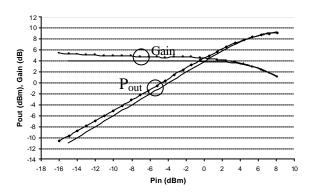

Finally, in order to validate the model, some large signal measurements have been carried out. For this purpose, we have applied at the input of the device a microwave power  $P_{in}$  using a 50  $\Omega$  generator and measured the output power  $P_{out}$  absorbed by the 50  $\Omega$  load (Fig.5) [9]. The results are shown in Fig.6.a and a good agreement has been observed with the large signal simulation made using ADS.

Fig. 5 Schematic measurement setup used for determination of the one tone power response of the device.

Fig. 6.a Output power Pout and gain versus input power on the transistor with W=8x12.5 µm. f=4 GHz, Vgs=1.5 V, Vds=2 V. Measurements (symbols) and model (solid line).

The scalability of the model in large signal condition versus gate width W has been checked as well on Fig.6.b, where we present the  $P_{out}$  versus  $P_{in}$  of the transistor with  $W=8x12.5~\mu m$  scaled at  $W=8x6.25~\mu m$ , and we compare it to the measured data of a transistor with  $W=8x6.25~\mu m$  (same frequency and biases).

Fig. 6.b Output power Pout and gain versus input power on the transistor. Measurements (symbols) and model (solid line).

#### **CONCLUSIONS**

In this paper a new empirical non-linear model for SOI MOSFET's (FD and PD) has been presented. This model is based both upon close form expressions of the non-linear drain current and gate charge. The parameters of the model can be easily extracted using ICCAP optimiser and the comparisons in terms of static and dynamic performances

are in good agreement with the experimental ones. Finally, single tone large signal measurements have been made and compared with simulations. As a conclusion, this non-linear model can be useful for the design of centimetrique and millimetrique non-linear circuits (mixers or oscillators).

## ACKNOWLEDGEMENT

The authors thank S. Lepillier for the technical support upon RF measurements. They also thank the LETI for providing devices.

#### REFERENCES

- [1] J.P. Collinge, J.Chen, D.Flandre, J.P.Raskin, R.Gillon and D.Vanhoenacker, "A Low-Voltage, Low-Power Microwave SOI MOSFET," SOI Conference, Proceedings, IEEE International, pp. 128 - 129, 30 Sept.-3 Oct. 1996

- [2] B.Iñiguez, L.F.Ferreira, B.Gentinne and D.Flandre, "A Physically-Based C<sub>∞</sub> Continuous Fully-Depleted SOI MOSFET Model for Analog Applications," *IEEE Trans. on Electron Devices*, vol. 43, pp. 568-575, no. 4, April 1996.

- [3] M.Vanmackelberg et al, "0.25 μm Fully Depleted SOI MOSFET's for RF Mixed Analog-Digital Circuits, Including a Comparison with Partially Depleted Devices with Relation to High Frequency Noise Parameters," *Solid-State Electronics*, vol. 46, pp. 379-386, 2002.

- [4] I.Angelov, H.Zirath and N.Rorsman, "A New Empirical Nonlinear Model for HEMT and MESFET Devices," *IEEE Trans. on Microwave Theory and Techniques*, vol. 40, no. 12, pp. 2258-2266, Dec. 1992.

- [5] D.E.Root, "Measurement-Based Large-Signal Device Modeling: a Conceptual Overview," *IEEE International Microwave Workshop on Nonlinear Modeling*, April 1999.

- [6] A.D. Snider, "Charge Conservation and the Transcapacitance Element: An Exposition," *IEEE Trans. on Education*, vol. 38, pp. 376-379, no. 4, Nov. 1995.

- [7] P.Antognetti and G.Massobrio, "Semiconductor Device Modeling with SPICE," New-York McGraw-Hill, 1988.

- [8] G.Dambrine, A.Cappy, F.Heliodore and E.Playez, "A New Method for Determining the FET Small-Signal Equivalent Circuit," *IEEE Trans. Microwave Theory Technologies*, vol. 36, pp. 1151-1159, July 1988.

- [9] N.Vellas, C.Gaquiere, F.Bue, Y.Guel, B.Boudard, J.C.deJaeger, and M.A.Poisson, "Load Impedance Influence on the I<sub>D</sub>(V<sub>DS</sub>) Characteristics of AlGaN/GaN HEMTs in Large Signal Regime at 4 GHz," *IEEE Electron Device Letters*, vol. 23, NO. 5, pp. 246-248, May 2002.